#### **iPLUG**

#### **Deliverable D3.2**

# Prototype Development, Experimental Validation, and Evaluation of LV Multiport Converters

### **Document information**

Deliverable nr D3.2

Deliverable Name Prototype Development, Experimental Validation, and Evaluation

of Low-Voltage Multiport Converters

Version 01

Release date 06/06/2025

Dissemination level Public

Status Submitted

Author Ahmed Yahia Farag Abdelfattah, Paolo Mattavelli,

Khaled Awadallah Ahmed Mohamed (UNIPD)

Mohammed Debbat (IREC)

# **Document history:**

| Version | Date of issue | Content and changes                           | Edited by   |

|---------|---------------|-----------------------------------------------|-------------|

| 01      | 07/05/2025    | First draft of the deliverable                | UNIPD       |

| 02      | 27/05/2025    | Revision                                      | Typhoon HIL |

| 03      | 30/05/2025    | Revised version and added conclusions section | UNIPD       |

| 04      | 05/06/2025    | Updated list of publications                  | UNIPD       |

## Peer reviewed by:

| Partner     | Reviewer                          |

|-------------|-----------------------------------|

| Typhoon HIL | Sergio Costa<br>Milan Arsenijevic |

| СТН         | Mebtu Beza                        |

## **Deliverable beneficiaries:**

| WP / t   | ask   |

|----------|-------|

| WP3/T3.3 | &T3.4 |

# **Table of contents**

| 1 | Exe  | ecutive Summary                                                                 | 16 |

|---|------|---------------------------------------------------------------------------------|----|

| 2 | Inti | roduction                                                                       | 18 |

|   | 2.1  | Background and Motivations for Multiport Converters                             | 18 |

|   | 2.2  | Scope of WP3 Research Activities                                                | 20 |

|   | 2.3  | Interrelations with WP3 Previous Deliverable (D3.1)                             | 22 |

|   | 2.4  | Interrelations with Other WPs in the iPlug Project                              | 22 |

|   | 2.5  | Summary of Contributions in This Deliverable                                    | 24 |

|   |      | 2.5.1 Experimental Prototype Development for the Proposed Multiport Con-        |    |

|   |      | verters                                                                         | 24 |

|   |      | 2.5.2 Experimental Validation of the Proposed Symmetric and Asymmetric          |    |

|   |      | Multiport Y-converters                                                          | 24 |

|   |      | 2.5.3 Performance Evaluation of Multiport Y-Converters using Renewable Source   | !  |

|   |      | Mission Profile                                                                 | 25 |

|   |      | 2.5.4 Proposing Nonlinear Control of Y-Converters for Grid Integration of 400 V |    |

|   |      | DC Microgrids                                                                   | 26 |

|   | 2.6  | List of Publications                                                            | 26 |

| 3 | Exp  | perimental Verification of the Multiport Y-Converter                            | 29 |

|   | 3.1  | Brief Analysis and Background                                                   | 29 |

|   |      | 3.1.1 Derivation and Operation Principle                                        | 29 |

|   |      | 3.1.2 Analysis and Fundamental Relations                                        | 30 |

|   |      | 3.1.2.1 Buck Mode                                                               | 30 |

|   |      | 3.1.2.2 Boost Mode                                                              | 32 |

|   | 3.2  | Description of the Experimental prototype                                       | 33 |

|   |      | 3.2.1 Semiconductor devices                                                     | 34 |

|   |      | 3.2.2 Control architecture                                                      | 36 |

|   |      | 3.2.3 Magnetic components                                                       | 36 |

|   |      | 3.2.4 Power supplies                                                            | 37 |

|   |      | 3.2.5 Power Meter                                                               | 37 |

|   |      | 3.2.6 Oscilloscope                                                              | 38 |

|   | 3.3  | Experimental Results                                                            | 38 |

| 4 | Exp  | perimental Verification of the Asymmetric Multiport Y-Converter                 | 42 |

|   | -    | Principle of Operation and Analysis                                             | 42 |

|   |      | 4.1.1 Mode I ( $V_{dc1} < V_{dc2}$ )                                            | 44 |

|   |      | 4.1.2 Mode II $(V_{dc1} > V_{dc2})$                                             | 46 |

|   | 4.2 | Minimization of the Low-frequency Voltage Ripples at the DC ports              | 47 |

|---|-----|--------------------------------------------------------------------------------|----|

|   | 4.3 | Experimental Results                                                           | 49 |

|   | 4.4 | Steady-State Experimental Results                                              | 51 |

|   |     | 4.4.1 Mode I ( $V_{dc1} < V_{dc2}$ )                                           | 51 |

|   |     | 4.4.2 Mode II ( $V_{dc1} > V_{dc2}$ )                                          | 53 |

|   |     | 4.4.3 Transient Experimental Results                                           | 56 |

|   |     | 4.4.3.1 Mode I ( $V_{dc1} < V_{dc2}$ )                                         | 56 |

|   |     | 4.4.4 Mode II ( $V_{dc1} > V_{dc2}$ )                                          | 59 |

|   |     | 4.4.5 Efficiency Evaluation                                                    | 62 |

|   |     | 4.4.5.1 Mode I ( $V_{dc1} < V_{dc2}$ )                                         | 62 |

|   |     | 4.4.5.2 Mode II ( $V_{dc1} < V_{dc2}$ )                                        | 65 |

|   | 4.5 | Conclusion                                                                     | 66 |

| 5 | Per | formance Evaluation of Multiport Y-Converters using Renewable Source           |    |

|   |     | sion Profile                                                                   | 67 |

|   | 5.1 | Introduction                                                                   | 67 |

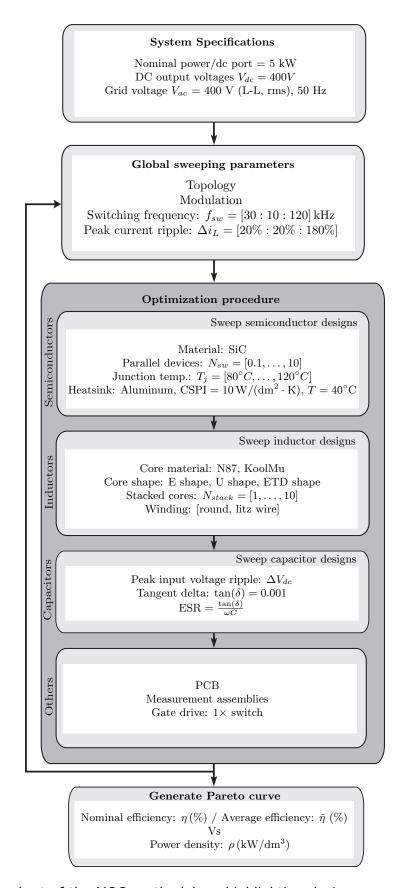

|   | 5.2 | Multi-Objective Optimization Procedure                                         | 69 |

|   |     | 5.2.1 Component Modeling                                                       | 70 |

|   |     | 5.2.1.1 Semiconductor Design                                                   | 70 |

|   |     | 5.2.1.2 Inductor Design                                                        | 70 |

|   |     | 5.2.1.3 Capacitor Design                                                       | 72 |

|   | 5.3 | Mission-Profile Efficiency Calculation Methodology                             | 72 |

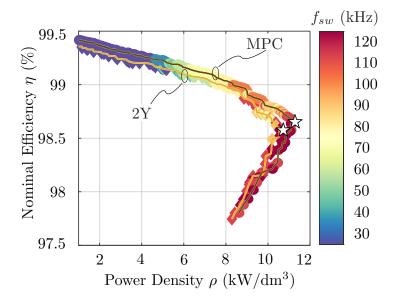

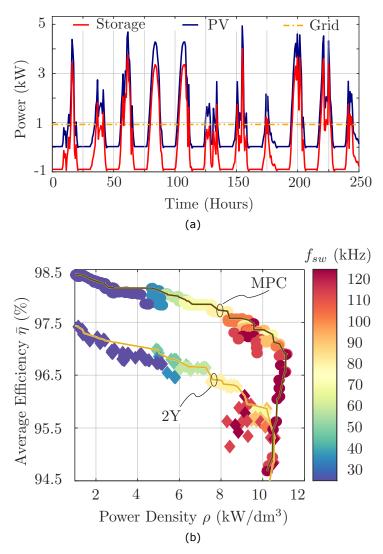

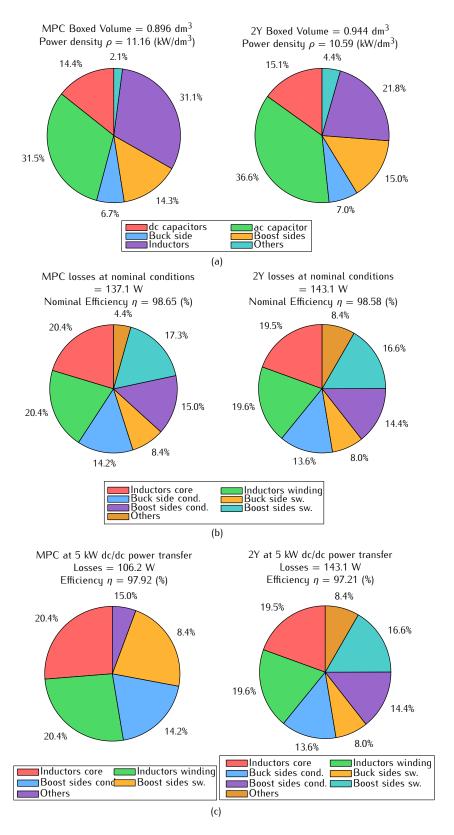

|   | 5.4 | Results and Discussion                                                         | 73 |

|   | 5.5 | Conclusion                                                                     | 77 |

| 6 | Nam | nlinear Control of the Y-Converters for Grid Integration of 400 V DC Mi-       |    |

| 0 |     | grids                                                                          | 78 |

|   |     | Introduction                                                                   | 78 |

|   |     | Analysis of the Y-Converter as loss-free resistor in sliding-mode control      | 79 |

|   | 0.2 | 6.2.1 Buck mode                                                                | 82 |

|   |     | 6.2.2 Boost mode                                                               | 83 |

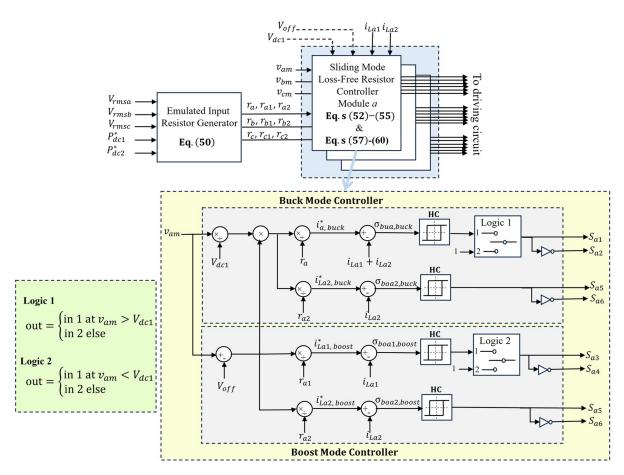

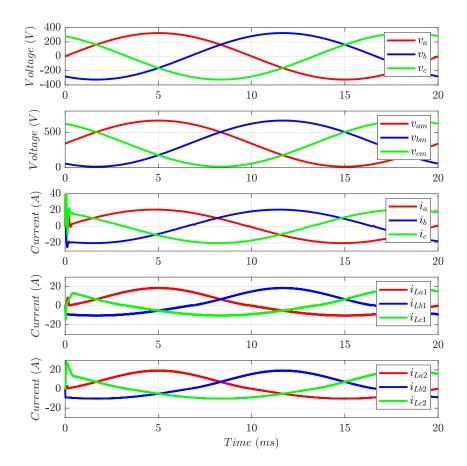

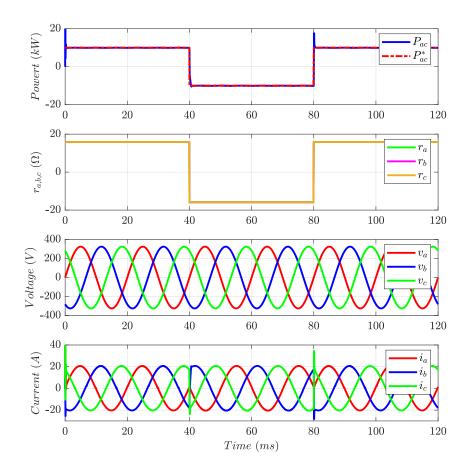

|   | 63  | Simulation Results                                                             | 84 |

|   | 0.5 | 6.3.1 Balanced ac grid conditions                                              | 84 |

|   |     | 6.3.2 Unbalanced ac grid conditions                                            | 86 |

|   | 6 1 | Extension of the proposed Nonlinear Controller to multiport converter scenario |    |

|   | 0.4 | 6.4.1 Buck Mode                                                                | 89 |

|   |     | 6.4.2 Boost Mode                                                               | 91 |

|   | 6 5 | Simulation Results                                                             |    |

|   | U.J | JIIIIuluull Nebulbaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaa                          | 22 |

| 7 | Conclusions    | 96 |

|---|----------------|----|

|   | 6.6 Conclusion | 95 |

# List of Figures

| 1  | Represintation of a Multiport converter interfacing various sources, loads and                                                     |    |

|----|------------------------------------------------------------------------------------------------------------------------------------|----|

|    | storages                                                                                                                           | 19 |

| 2  | Multiport converter for distribution level scenario                                                                                | 20 |

| 3  | Multiport converter for residential level scenario                                                                                 | 21 |

| 4  | WP1 case studies utilized in WP3 activities                                                                                        | 23 |

| 5  | A schematic of two-port and multiport Y-converters in a modular form: (a)                                                          |    |

|    | Two-port Y-converter; (b) The symmetric Multiport Y-converter                                                                      | 29 |

| 6  | Module $a$ of the proposed converter                                                                                               | 31 |

| 7  | Operation modes of one module of the proposed converter: (a) Buck mode                                                             |    |

|    | when $v_{am} > V_{dc1}$ ; (b) Boost mode when $v_{am} < V_{dc1}$                                                                   | 31 |

| 8  | Key waveforms of module $a$ of the proposed converter                                                                              | 33 |

| 9  | Picture of the experimental prototype of the proposed converter                                                                    | 35 |

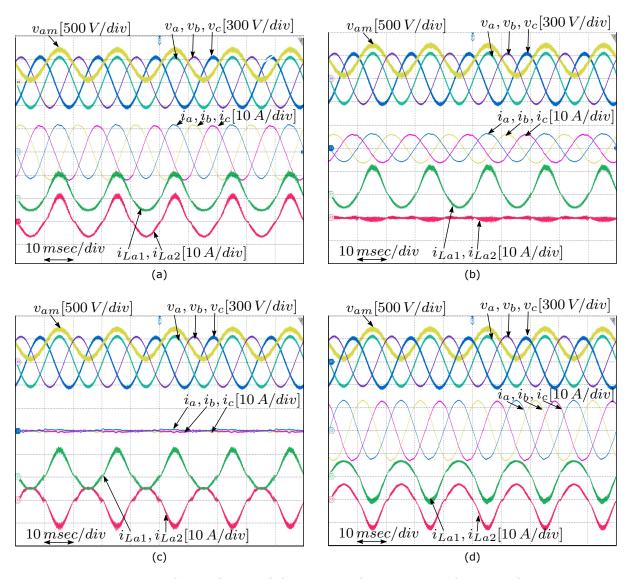

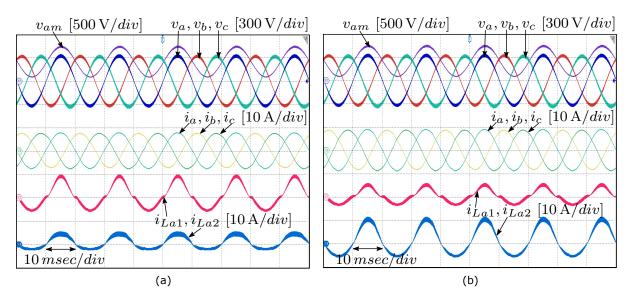

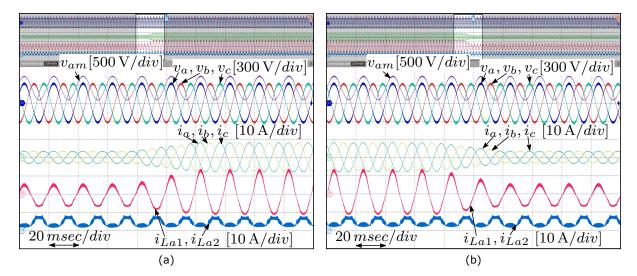

| 10 | Experimental waveforms of the proposed converter with $V_{dc1}$ and $V_{dc2}$ are set                                              |    |

|    | to $360\mathrm{V}$ and $400\mathrm{V}$ under different values of $P_{dc1}$ and $P_{dc2}$ : (a) $P_{dc1}$ and $P_{dc2}$ both        |    |

|    | equal to $3\mathrm{kW}$ ; (b) $P_{dc1}$ and $P_{dc2}$ equal to $3\mathrm{kW}$ and $0\mathrm{kW}$ , respectively; (c) $P_{dc1}$     |    |

|    | and $P_{dc2}$ equal to $3\mathrm{kW}$ and $-3\mathrm{kW}$ , respectively; and (d) $P_{dc1}$ and $P_{dc2}$ equal to                 |    |

|    | -3 kW and $-3$ kW, respectively                                                                                                    | 39 |

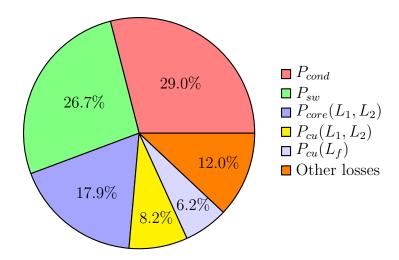

| 11 | Calculated losses breakdown of the experimental prototype at $P_{dc1}$ and $P_{dc2}$                                               |    |

|    | both equal to 3 kW                                                                                                                 | 40 |

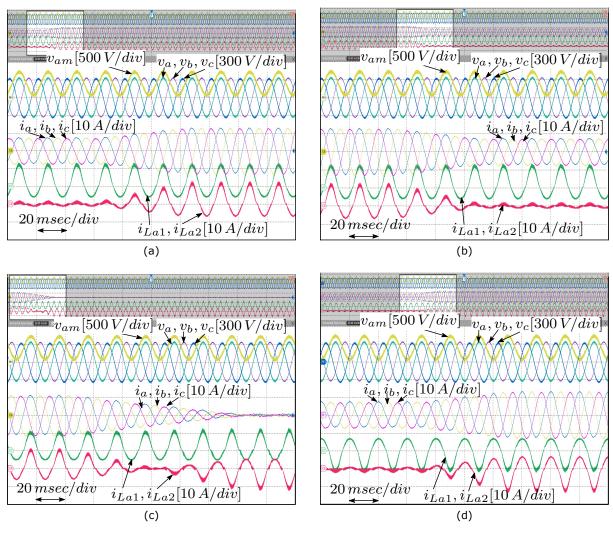

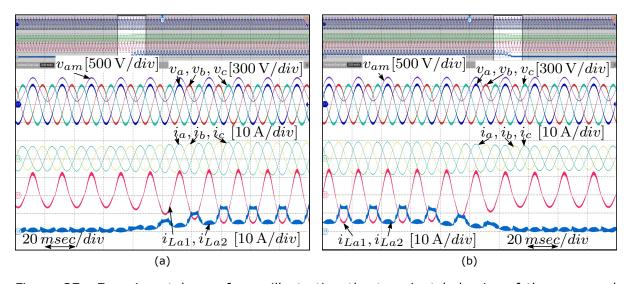

| 12 | Experimental waveforms illustrating the transient behavior of the experimental                                                     |    |

|    | prototype: (a) $P_{dc1}$ equal to $3\mathrm{kW}$ and $P_{dc2}$ increased from $0.3\mathrm{kW}$ to $3\mathrm{kW}$ ; (b)             |    |

|    | $P_{dc1}$ equal to $3\mathrm{kW}$ and $P_{dc2}$ decreased from $3\mathrm{kW}$ to $0.3\mathrm{kW}$ ; (c) $P_{dc1}$ equal to         |    |

|    | $3\mathrm{kW}$ and $P_{dc2}$ changed from $3\mathrm{kW}$ to $-3\mathrm{kW}$ ; (d) $P_{dc1}$ equal to $-3\mathrm{kW}$ and $P_{dc2}$ |    |

|    | changed from $-0.3\mathrm{kW}$ to $-3\mathrm{kW}$                                                                                  | 41 |

| 13 | Different configurations of the modular Y-converter: (a) The two-port Y-converte                                                   | r, |

|    | (b) The symmetric multiport Y-converter (Y-MPC), and (c) The asymmetric                                                            |    |

|    | multiport Y-converter (AY-MPC)                                                                                                     | 43 |

| 14 | Key waveforms of the proposed AY-MPC in different operating modes: (a)                                                             |    |

|    | Mode I: when $V_{dc1}$ is lower than $V_{dc2}$ and (b) Mode II: when $V_{dc1}$ is greater than                                     |    |

|    | $V_{dc2}$                                                                                                                          | 45 |

| 15 | Different waveforms of $i_{La2_{av}}$ to be analyzed for reducing the low-frequency                                                |    |

|    | voltage ripples at the dc ports: (a) original waveform; (b) dc waveform; (c)                                                       |    |

|    | ideal waveform eliminating the low-frequency voltage ripples; and (d) clamped                                                      |    |

|    | waveform. The waveforms are not to scale                                                                                           | 48 |

| 16 | Different waveforms of $i_{La2}$ and their corresponding $i_{La1}$ to to maintain bal-                                               |    |

|----|--------------------------------------------------------------------------------------------------------------------------------------|----|

|    | anced ac grid currents: (a) $i_{La2}$ original waveform; (b) $i_{La2}$ dc waveform; and                                              |    |

|    | (c) $i_{La2}$ clamped waveform                                                                                                       | 50 |

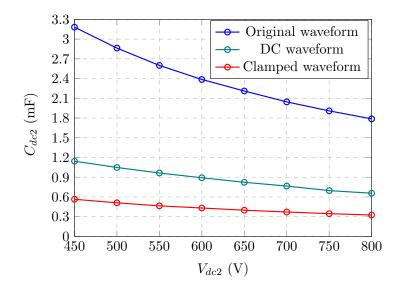

| 17 | Required $C_{dc2}$ for the three $i_{La2_{av}}$ waveforms with $V_{dc1}$ is fixed at $400\mathrm{V}$ , $P_{dc1}$ and                 |    |

|    | $P_{dc2}$ are set to $3\mathrm{kW}$ and $1\mathrm{kW}$ , respectively                                                                | 51 |

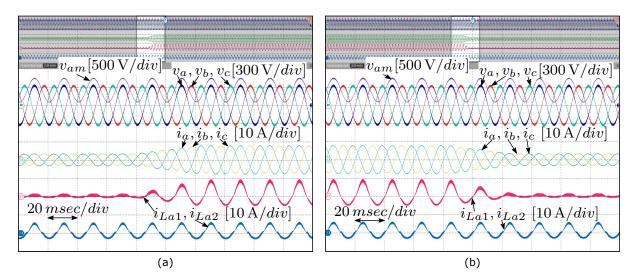

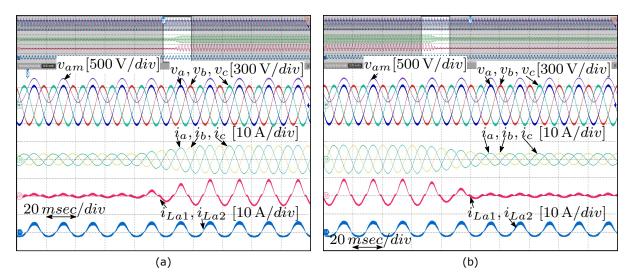

| 18 | Experimental waveforms of the proposed converter in Mode I, using the orig-                                                          |    |

|    | inal $i_{La2_{av}}$ waveform at different power levels, with $V_{dc1}$ and $V_{dc2}$ set to $400\mathrm{V}$                          |    |

|    | and $500\mathrm{V}$ , respectively: (a) $P_{dc1}$ equals $3\mathrm{kW}$ and $P_{dc2}$ equals $0.5\mathrm{kW}$ ; (b) $P_{dc1}$        |    |

|    | equals $3\mathrm{kW}$ and $P_{dc2}$ equals $1\mathrm{kW}$ ; and (c) $P_{dc1}$ equals $1.6\mathrm{kW}$ and $P_{dc2}$ equals           |    |

|    | 1 kW                                                                                                                                 | 52 |

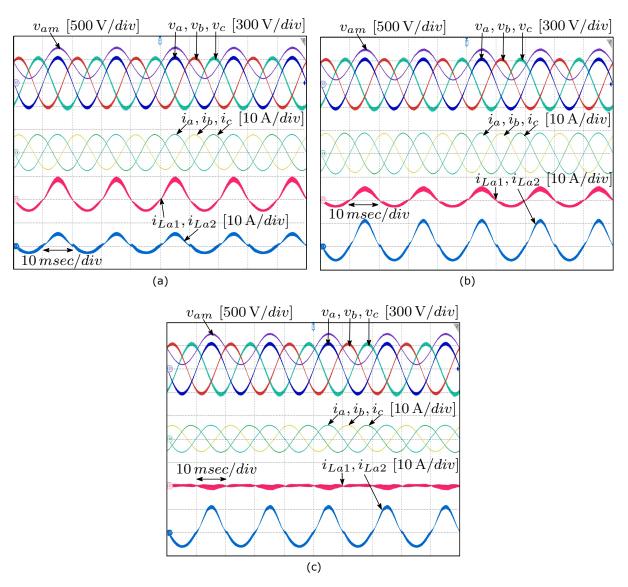

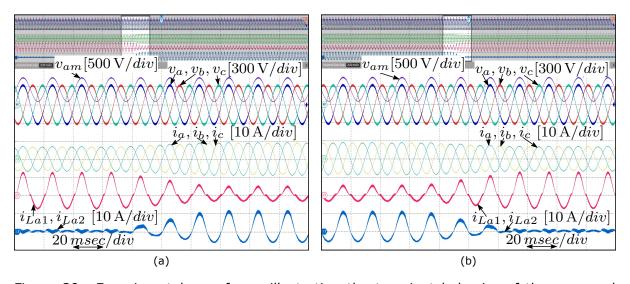

| 19 | Experimental waveforms of the proposed converter in Mode I, using the dc                                                             |    |

|    | $i_{La2_{av}}$ waveform at different power levels, with $V_{dc1}$ and $V_{dc2}$ set to $400\mathrm{V}$ and                           |    |

|    | $500\mathrm{V}$ , respectively: (a) $P_{dc1}$ equals $3\mathrm{kW}$ and $P_{dc2}$ equals $0.5\mathrm{kW}$ ; (b) $P_{dc1}$ equals     |    |

|    | $3\mathrm{kW}$ and $P_{dc2}$ equals $1\mathrm{kW}$ ; and (c) $P_{dc1}$ equals $1.6\mathrm{kW}$ and $P_{dc2}$ equals $1\mathrm{kW}$   | 54 |

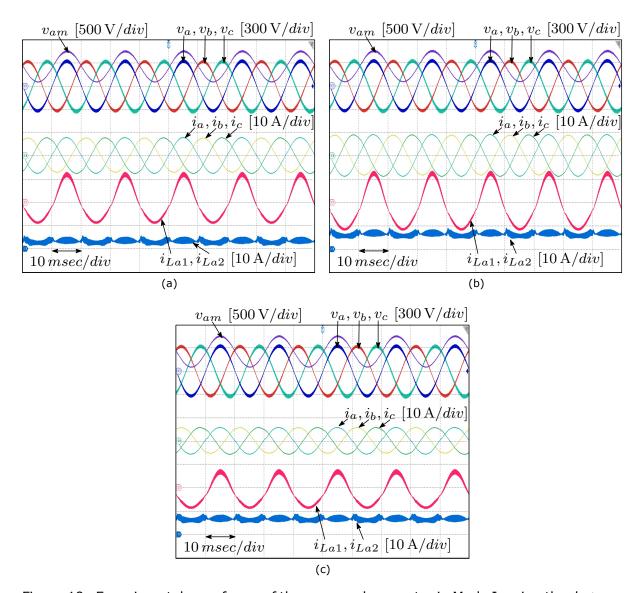

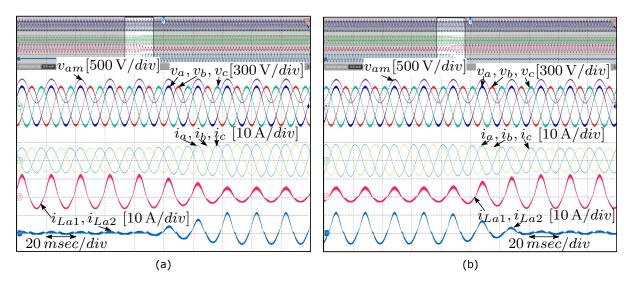

| 20 | Experimental waveforms of the proposed converter in Mode I, using the clamped                                                        |    |

|    | $i_{La2_{av}}$ waveform at different power levels, with $V_{dc1}$ and $V_{dc2}$ set to $400\mathrm{V}$ and                           |    |

|    | $500\mathrm{V}$ , respectively: (a) $P_{dc1}$ equals $3\mathrm{kW}$ and $P_{dc2}$ equals $0.5\mathrm{kW}$ ; (b) $P_{dc1}$ equals     |    |

|    | $3\mathrm{kW}$ and $P_{dc2}$ equals $1\mathrm{kW}$ ; and (c) $P_{dc1}$ equals $1.6\mathrm{kW}$ and $P_{dc2}$ equals $1\mathrm{kW}$   | 55 |

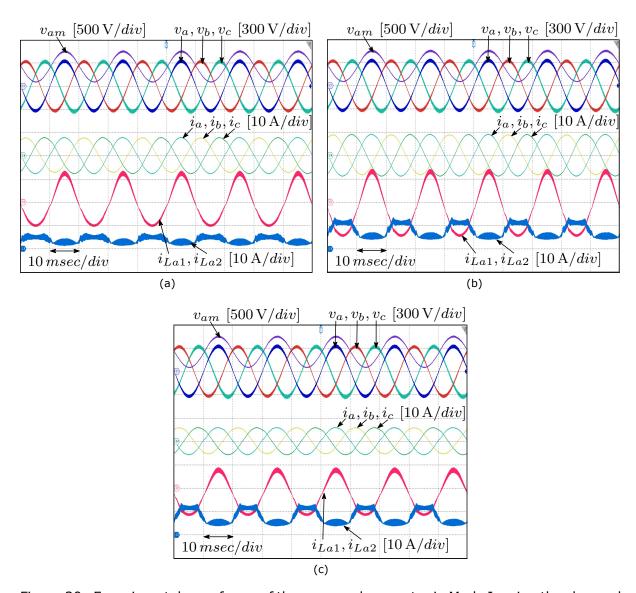

| 21 | Experimental waveforms of the proposed converter in Mode II, using the orig-                                                         |    |

|    | inal $i_{La2_{av}}$ waveform at different power levels, with $V_{dc1}$ and $V_{dc2}$ set to $400\mathrm{V}$                          |    |

|    | and $500\mathrm{V}$ , respectively: (a) $P_{dc1}$ equals $3\mathrm{kW}$ and $P_{dc2}$ equals $0.5\mathrm{kW}$ ; and (b)              |    |

|    | $P_{dc1}$ equals $3\mathrm{kW}$ and $P_{dc2}$ equals $1\mathrm{kW}.$                                                                 | 56 |

| 22 | Experimental waveforms illustrating the transient behavior of the proposed                                                           |    |

|    | converter in Mode I with the original $i_{La2_{av}}$ waveform at $V_{dc1}$ equals $400\mathrm{V}$ , $V_{dc2}$                        |    |

|    | equals $500\mathrm{V}$ , and $P_{dc1}$ equals $0.5\mathrm{kW}$ : (a) $P_{dc1}$ is increased from $1\mathrm{kW}$ to $3\mathrm{kW}$ ;  |    |

|    | and (b) $P_{dc1}$ is decreased from $3\mathrm{kW}$ to $1\mathrm{kW}$                                                                 | 57 |

| 23 | Experimental waveforms illustrating the transient behavior of the proposed                                                           |    |

|    | converter in Mode I with the original $i_{La2_{av}}$ waveform at $V_{dc1}$ equals $400\mathrm{V}$ , $V_{dc2}$                        |    |

|    | equals $500\mathrm{V}$ , and $P_{dc1}$ equals $3\mathrm{kW}$ : (a) $P_{dc2}$ is increased from $0.1\mathrm{kW}$ to $1\mathrm{kW}$ ;  |    |

|    | and (b) $P_{dc2}$ is decreased from $1\mathrm{kW}$ to $0.1\mathrm{kW}.$                                                              | 58 |

| 24 | Experimental waveforms illustrating the transient behavior of the proposed                                                           |    |

|    | converter in Mode I with the dc $i_{La2_{av}}$ waveform at $V_{dc1}$ equals $400\mathrm{V}$ , $V_{dc2}$ equals                       |    |

|    | $500\mathrm{V}$ , and $P_{dc1}$ equals $0.5\mathrm{kW}$ : (a) $P_{dc1}$ is increased from $1\mathrm{kW}$ to $3\mathrm{kW}$ ; and (b) |    |

|    | $P_{dc1}$ is decreased from $3\mathrm{kW}$ to $1\mathrm{kW}$                                                                         | 58 |

| 25 | Experimental waveforms illustrating the transient behavior of the proposed                                                           |    |

|----|--------------------------------------------------------------------------------------------------------------------------------------|----|

|    | converter in Mode I with the dc $i_{La2_{av}}$ waveform at $V_{dc1}$ equals $400\mathrm{V}$ , $V_{dc2}$ equals                       |    |

|    | $500\mathrm{V}$ , and $P_{dc1}$ equals $3\mathrm{kW}$ : (a) $P_{dc2}$ is increased from $0.1\mathrm{kW}$ to $1\mathrm{kW}$ ; and (b) |    |

|    | $P_{dc2}$ is decreased from 1 kW to $0.1$ kW                                                                                         | 59 |

| 26 | Experimental waveforms illustrating the transient behavior of the proposed                                                           |    |

|    | converter in Mode I with the clamped $i_{La2_{av}}$ waveform at $V_{dc1}$ equals $400\mathrm{V}$ , $V_{dc2}$                         |    |

|    | equals $500\mathrm{V}$ , and $P_{dc1}$ equals $0.5\mathrm{kW}$ : (a) $P_{dc1}$ is increased from $1\mathrm{kW}$ to $3\mathrm{kW}$ ;  |    |

|    | and (b) $P_{dc1}$ is decreased from $3\mathrm{kW}$ to $1\mathrm{kW}$                                                                 | 60 |

| 27 | Experimental waveforms illustrating the transient behavior of the proposed                                                           |    |

|    | converter in Mode I with the clamped $i_{La2_{av}}$ waveform at $V_{dc1}$ equals $400\mathrm{V}$ , $V_{dc2}$                         |    |

|    | equals $500\mathrm{V}$ , and $P_{dc1}$ equals $3\mathrm{kW}$ : (a) $P_{dc2}$ is increased from $0.1\mathrm{kW}$ to $1\mathrm{kW}$ ;  |    |

|    | and (b) $P_{dc2}$ is decreased from $1\mathrm{kW}$ to $0.1\mathrm{kW}\dots\dots\dots\dots\dots\dots$                                 | 60 |

| 28 | Experimental waveforms illustrating the transient behavior of the proposed                                                           |    |

|    | converter in Mode II with the original $i_{La2_{av}}$ waveform at $V_{dc1}$ equals $400\mathrm{V}$ , $V_{dc2}$                       |    |

|    | equals $500\mathrm{V}$ , and $P_{dc1}$ equals $0.5\mathrm{kW}$ : (a) $P_{dc1}$ is increased from $1\mathrm{kW}$ to $3\mathrm{kW}$ ;  |    |

|    | and (b) $P_{dc1}$ is decreased from $3\mathrm{kW}$ to $1\mathrm{kW}$                                                                 | 61 |

| 29 | Experimental waveforms illustrating the transient behavior of the proposed                                                           |    |

|    | converter in Mode I with the original $i_{La2_{av}}$ waveform at $V_{dc1}$ equals $400\mathrm{V}$ , $V_{dc2}$                        |    |

|    | equals $500\mathrm{V}$ , and $P_{dc1}$ equals $3\mathrm{kW}$ : (a) $P_{dc2}$ is increased from $0.1\mathrm{kW}$ to $1\mathrm{kW}$ ;  |    |

|    | and (b) $P_{dc2}$ is decreased from $1\mathrm{kW}$ to $0.1\mathrm{kW}.$                                                              | 61 |

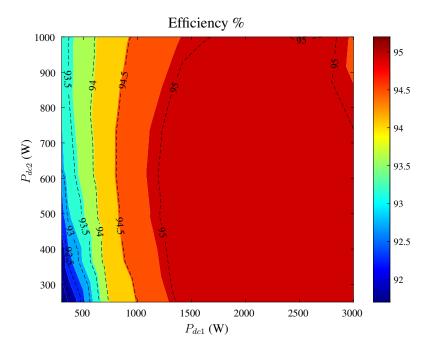

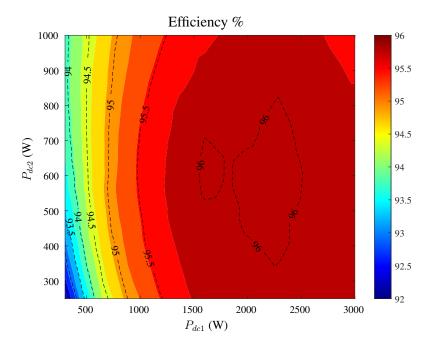

| 30 | Measured prototype efficiency for different values of $\mathcal{P}_{dc1}$ and $\mathcal{P}_{dc2}$ when op-                           |    |

|    | erating in Mode I with the original $i_{La2_{av}}$ waveform at $V_{dc1}$ equals $400\mathrm{V}$ , $V_{dc2}$                          |    |

|    | equals 500 V                                                                                                                         | 62 |

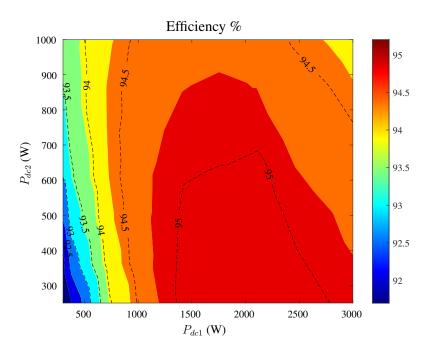

| 31 | Measured prototype efficiency for different values of $\mathcal{P}_{dc1}$ and $\mathcal{P}_{dc2}$ when op-                           |    |

|    | erating in Mode I with the dc $i_{La2_{av}}$ waveform at $V_{dc1}$ equals $400\mathrm{V}$ , $V_{dc2}$ equals                         |    |

|    | 500 V                                                                                                                                | 63 |

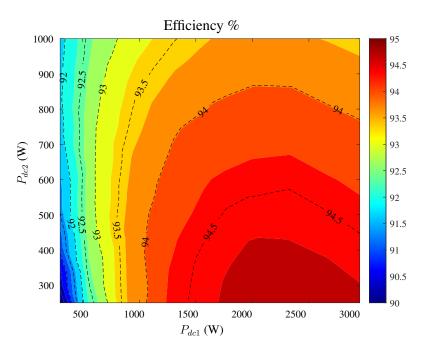

| 32 | Measured prototype efficiency for different values of $\mathcal{P}_{dc1}$ and $\mathcal{P}_{dc2}$ when op-                           |    |

|    | erating in Mode I with the clamped $i_{La2_{av}}$ waveform at $V_{dc1}$ equals $400\mathrm{V}$ , $V_{dc2}$                           |    |

|    | equals 500 V                                                                                                                         | 63 |

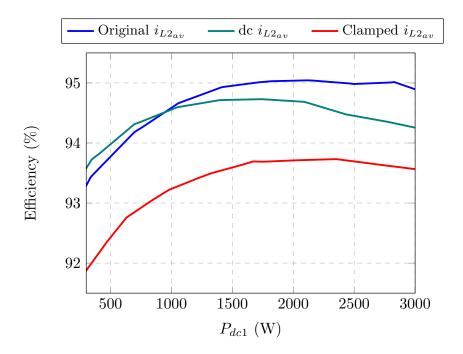

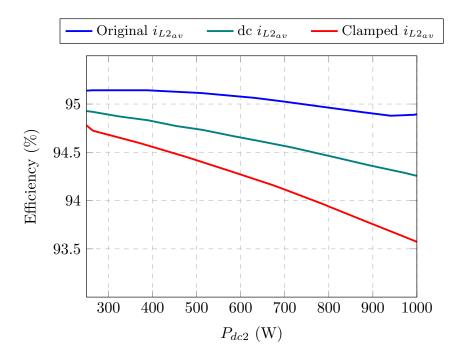

| 33 | Efficiency comparison of the proposed converter in Mode I with different $i_{L2_{av}}$                                               |    |

|    | wavefroms. The efficiency is evaluated across a range of $P_{dc1}$ values at $P_{dc2}$                                               |    |

|    | equals $1  \text{kW}$ , $V_{dc1}$ equals $400  \text{V}$ , and $V_{dc2}$ equals $500  \text{V}$                                      | 64 |

| 34 | Efficiency comparison of the proposed converter in Mode I with different $i_{L2_{av}}$                                               |    |

|    | wavefroms. The efficiency is evaluated across a range of $P_{dc2}$ values at $P_{dc1}$                                               |    |

|    | equals $3  \text{kW}$ , $V_{dc1}$ equals $400  \text{V}$ , and $V_{dc2}$ equals $500  \text{V}$                                      | 65 |

| 35 | Measured prototype efficiency for different values of $\mathit{P}_{dc1}$ and $\mathit{P}_{dc2}$ when op-     |    |

|----|--------------------------------------------------------------------------------------------------------------|----|

|    | erating in Mode II with the original $i_{La2_{av}}$ waveform at $V_{dc1}$ equals $500\mathrm{V}$ , $V_{dc2}$ |    |

|    | equals $400\mathrm{V}.$                                                                                      | 66 |

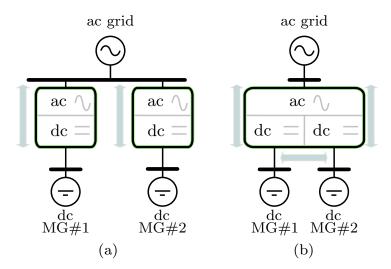

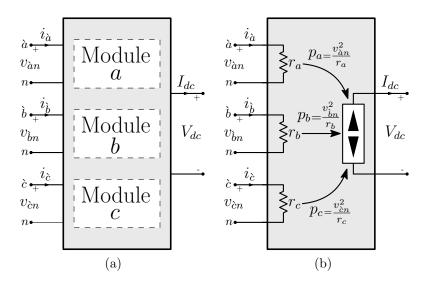

| 36 | ac grid integration of two dc MGs: (a) separate two-port converters vs. (b)                                  |    |

|    | multiport converter                                                                                          | 67 |

| 37 | Schematics of the evaluated topologies: (a) two port Y-converter; (b) multi-                                 |    |

|    | port Y-converter (MPC)                                                                                       | 69 |

| 38 | Flowchart of the MOO methodology highlighting design space exploration and                                   |    |

|    | Pareto front generation                                                                                      | 71 |

| 39 | Pareto-front evaluation of both designs considering nominal efficiency                                       | 73 |

| 40 | Mission-profile based evaluation of both configurations: (a) The Mission profile                             |    |

|    | adopted in the evaluation; (b) Pareto-front evaluation of both designs consid-                               |    |

|    | ering average efficiency                                                                                     | 74 |

| 41 | (a) Components' volume distribution at the maximum power-density points.                                     |    |

|    | (b) Power loss distribution across converter components at the maximum                                       |    |

|    | power-density points. (c) dc-dc power transfer loss comparison between MPC                                   |    |

|    | and 2Y topologies                                                                                            | 75 |

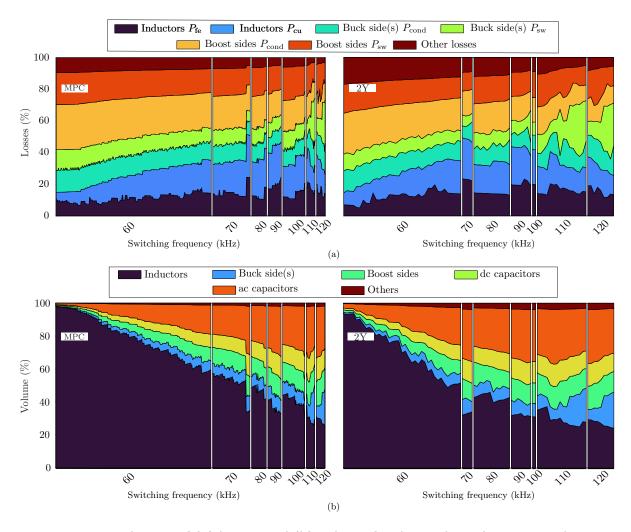

| 42 | Distribution of (a) losses and (b) volume for the evaluated converter designs.                               | 76 |

| 43 | Schematic of the four-wire Y-converter                                                                       | 79 |

| 44 | The Four-wire Y-converter emulated as loss-free resistors: a) Tetra-port cir-                                |    |

|    | cuit; b) Loss-free resistor circuits with highlighting the instantaneous power                               |    |

|    | transferred from each phase to the dc MG                                                                     | 80 |

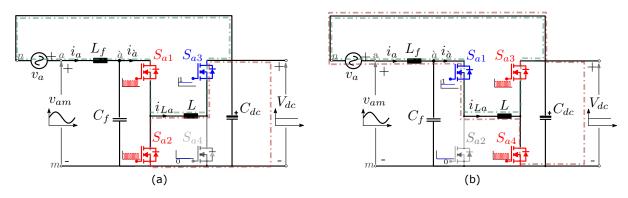

| 45 | Operation modes of module $\it a$ of the 4-W Y-converter including current paths:                            |    |

|    | (a) Buck mode ( $v_{am} > V_{dc}$ ); (b) Boost mode ( $v_{am} < V_{dc}$ )                                    | 82 |

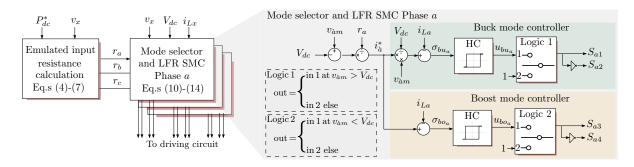

| 46 | Overall block diagram of the proposed controller, featuring a detailed illustra-                             |    |

|    | tion of the mode selector and the LFR based on SMC for phase $a$ , with key                                  |    |

|    | equations highlighted                                                                                        | 83 |

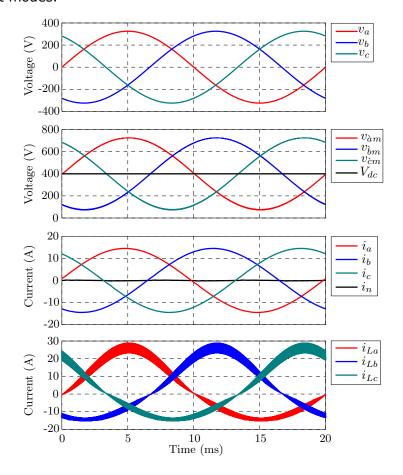

| 47 | Simulation results of the proposed controller operating at nominal power under                               |    |

|    | balanced ac grid conditions                                                                                  | 85 |

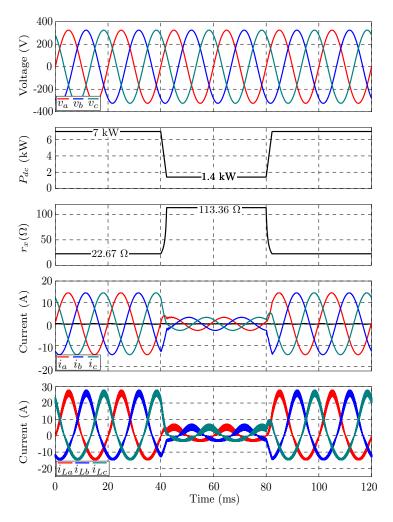

| 48 | Transient simulation results of the proposed controller under balanced ac grid                               |    |

|    | conditions. The power steps from nominal to 20% after two grid periods and                                   |    |

|    | returns to nominal after two more                                                                            | 86 |

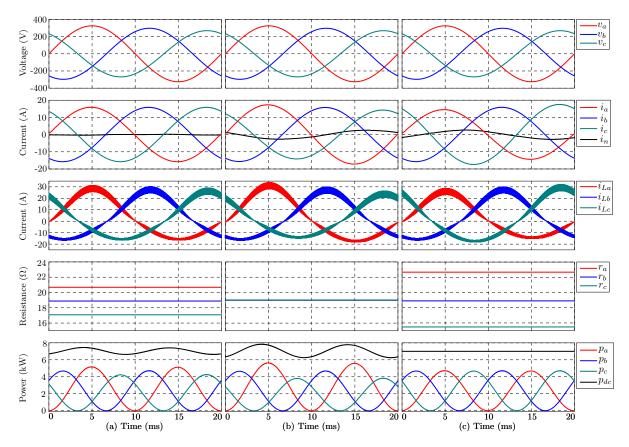

| 49 | Simulation results of the proposed controller operating at nominal power under  |    |

|----|---------------------------------------------------------------------------------|----|

|    | unbalanced ac grid conditions: (a) constant input current mode; (b) constant    |    |

|    | input resistance mode; and (c) constant input power mode. The waveforms il-     |    |

|    | lustrate the independent control of the emulated resistances in different modes |    |

|    | and highlight the advantage of the constant input power mode in eliminating     |    |

|    | power fluctuations at the dc MG during unbalanced symmetric ac grid voltages.   | 87 |

| 50 | A schematic of multiport Y-converters in a modular form                         | 88 |

| 51 | Multiport Y-converter emulated as LFR: a) Tetra-port circuit, b) LFR circuit    | 89 |

| 52 | Module $a$ of the multiport Y-converter                                         | 90 |

| 53 | Operation modes of one module of the proposed converter: (a) Buck mode          |    |

|    | when $v_{am} > V_{dc1}$ ; (b) Boost mode when $v_{am} < V_{dc1}$                | 90 |

| 54 | Block diagram of the proposed controller                                        | 93 |

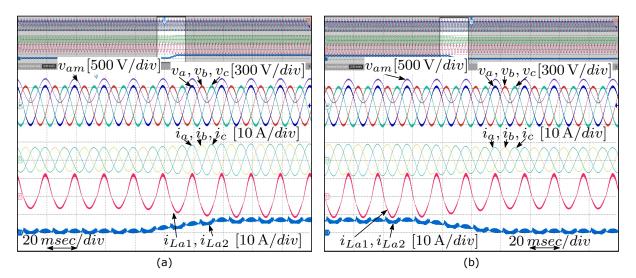

| 55 | Steady-state simulation results of the proposed controller operating at nominal |    |

|    | power under balanced AC grid conditions                                         | 94 |

| 56 | Simulation results of the proposed controller illustrating transient behavior   |    |

|    | under balanced AC grid conditions                                               | 95 |

# **List of Tables**

| 1 | Summary of the basic equations of the proposed converter                                    | 34 |

|---|---------------------------------------------------------------------------------------------|----|

| 2 | $\operatorname{SiC}$ devices and passive components utilized in the experimental prototype. | 38 |

| 3 | Summary of the basic equations of the proposed converter                                    | 47 |

| 4 | Key parameters of the Four-Wire Y-converter                                                 | 84 |

| 5 | Key parameters of the Multiport Y-converter used in the simulation results                  | 93 |

## **List of Acronyms**

4-W Four-Wire

ac Alternating Current

ADC Analog-to-Digital Converter

BPF Band-Pass Filter

CMV Common-Mode Voltage

CSC Current Source Converter

CSPI Cooling System Performance Index

dc Direct Current

DER Distributed Energy Resource

DN Distribution Network

EMI Electromagnetic Interference

ESR Effective Series Resistance

ESS Energy Storage System

ESOP Enhanced SOFT Open Point

EV Electric Vehicle

EU European Union

FFS Fixed-Frequency Sampling

FPGA Field Programmable Gate Array

LDO Low Drop-Out (Regulator)

LED Light Emitting Diode

LFR Loss-Free Resistor

LPF Low-Pass Filter

MG Microgrid

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

MPC Multiport Converter

MOO Multi-Objective Optimization

PCB Printed Circuit Board

PLL Phase-Locked Loop

POPI Power Output Port Interface

PFC Power Factor Correction

PV Photovoltaic

PWM Pulse-Width Modulation

RC Resistor-Capacitor

RES Renewable Energy Source RCP Rapid Control Prototyping

RMS Root Mean Square

RTOS Real-Time Operating System

SMC Sliding-Mode Control

SiC MOSFET Silicon Carbide Metal-Oxide-Semiconductor Field-Effect Transistor

THD Total Harmonic Distortion

TSSOP Thin Shrink Small Outline Package

VCO Voltage-Controlled Oscillator

VSC Voltage Source Converter

WP Work Package

ZVS Zero-Voltage Switching

#### **List of Nomenclatures**

$C_f$ Input capacitor

$\Delta P_{2}$

$C_{dc1}, C_{dc2}$ dc capacitor connected to port 1 and port 2, respectively

$d_{Bu_x}$ Duty cycle of the buck half-bridge

Duty cycle of the first boost half-bridge  $d_{Bo_{a1}}$

Duty cycle of the second boost half-bridge  $d_{Bo_{a2}}$

$\Delta P_1$ Power step size for Port 1 Power step size for Port 2

Turn-on switching energy loss  $E_{\mathsf{on}}$

Turn-off switching energy loss  $E_{\mathsf{off}}$

Switching frequency  $f_{sw}$

AC grid current at phase a  $i_a$ AC grid current at phase b  $i_b$ AC grid current at phase c $i_c$

Current through the input capacitor of module a  $i_{Cf,a}$ Average inductor current of inductor  $L_1$  in module a $i_{La1,av}$ Average inductor current of inductor  $L_2$  in module a $i_{La2,av}$  $L_1, L_2$ Main Inductors of dc port 1 and dc port 2, respectively

$L_f$ Grid-side filter inductor  $P_{\mathsf{ac}}$ Fixed ac port power Total power to dc side  $P_{\mathsf{dc}}$

$P_{dc1}$ Power at dc Port 1 Power at dc Port 2  $P_{\mathsf{dc2}}$

Rated power of dc Port 1  $P_{\mathsf{dc,rated1}}$ Rated power of dc Port 2  $P_{\mathsf{dc,rated2}}$

$P_{\sf op}(t)$ Instantaneous operating power

$P_{PV}(t)$ PV power profile over time

Power at storage port  $P_{\mathsf{storage}}(t)$

Power delivered by module x (x = a, b, c)  $P_x$

Iron losses in inductors  $P_{\mathsf{fe}}$  $P_{\mathsf{cu}}$ Copper losses in inductors

Semiconductor conduction losses  $P_{\mathsf{cond}}$ Semiconductor switching losses  $P_{\mathsf{SW}}$

Total power from ac side  $P_{\mathsf{ac}}$

on-state resistance of MOSFET  $R_{\mathsf{DS}}$

Emulated input resistance of module x $r_x$

$T_i$  Semiconductor junction temperature

$V_{\mathsf{DS}}$  Drain-source voltage

$V_{\mathsf{RMS}x}$  RMS value of phase voltage x

$V_{dc}$  DC-side voltage

$V_{dc1}$  DC voltage at port 1  $V_{dc2}$  DC voltage at port 2

$V_{\rm off}$  Offset voltage

$\hat{I}_m$  Peak phase current

$\hat{I}_{m1}$  Equivalent reference peak phase current from DC MG#1  $\hat{I}_{m2}$  Equivalent reference peak phase current from DC MG#2

$\hat{V}_m$  Peak value of AC grid phase voltage  $\omega$  AC grid angular frequency (rad/s)

$heta_x$  Phase angle of voltage  $v_x$

$v_x$  AC grid phase voltage at  $x \in \{a, b, c\}$

$v_{am}$ ,  $v_{bm}$ ,  $v_{cm}$  AC-side module voltages for modules a, b, and c

## 1 Executive Summary

The EU's commitment to net-zero greenhouse gas emissions by 2050 necessitates rapid deployment of power converter-interfaced devices in electric power systems. This includes renewable energy sources (RESs) and energy storage systems (ESSs) in distribution networks (DNs). Traditional two-port power converters often fail to meet demand profiles effectively, leading to significant voltage fluctuations during generation-demand imbalances, particularly in radial feeders.

Multiport Converters (MPCs) provide an effective solution by integrating multiple energy ports into a single aggregated hub, offering high controllability and efficient energy management across all ports while maintaining power quality and grid stability. MPCs can address DN challenges by reducing conversion stages, leading to cost-efficiency and higher power density. MPCs offer flexibility in selecting the number of ports and their characteristics (AC or DC), making them ideal energy hubs for connecting feeders, substations, RESs, and ESSs. Compared to conventional systems composed of multiple individual interfacing converters, MPCs provide lower system cost, reduced size, and higher power density. Advanced controllability, communication, and computational capabilities in MPCs support future smart grids by decentralizing decision-making processes, enabling rapid responses, and holistic control to enhance overall grid performance.

WP3 focuses on investigating and enabling MPCs in low-voltage (LV) DNs, addressing challenges such as developing efficient and compact circuit topologies for interfacing three-phase and single-phase AC systems with multiple DC ports. This will enhance converter efficiency, improve power density, and reduce component counts by minimizing conversion stages. Additionally, control and modulation constraints will be addressed to ensure Zero-Voltage-Switching (ZVS) and reduce passive reactive elements to boost power density. High-performance current and voltage control techniques will maintain control bandwidth and impedance passivity across all ports, reducing dynamic instability and transient oscillations in future distribution grids.

At the distribution level, DNs with significant penetration of renewable sources and various industrial loads require power electronics to facilitate the integration of renewables and ESSs, optimize network use, and connect loads at different voltage levels. Power-electronic solutions like ESOP, smart transformers, and MPCs enhance capacity, flexibility, and controllability in distribution grids. For residential areas, MPCs accommodate future connections of EVs and distributed renewable generation, improving load balance, voltages, and renewable capacity.

In household settings, MPCs link local RESs and ESSs with the distribution grid, supporting local energy storage systems and EVs. This enhances system efficiency and reduces

integration costs, optimizing energy management at the household level and contributing to the overall stability and efficiency of the distribution network.

This report, Deliverable 3.2 of the iPlug project, provides a comprehensive overview of the laboratory prototypes developed and the experimental validation conducted as part of WP3, which focuses on the investigation of multiport converters (MPCs) for LV applications. Building upon the foundations laid in the previous WP3 deliverable, D3.1 [1], which introduced innovative single-stage non-isolated MPC topologies tailored for residential use, this report emphasizes the experimental assessment of those proposed converter architectures under a wide range of realistic operating conditions.

In Sections 3 and 4, the experimental tests to validate the performance and efficiency of the proposed converters under steady-state and dynamic scenarios are presented, reflecting practical grid-interfacing and energy management requirements. Furthermore, this deliverable advances the evaluation of MPCs by incorporating a multi-objective optimization framework. The optimization simultaneously targets high efficiency and elevated power density—two critical metrics for compact and cost-effective power conversion systems. The results demonstrate the ability of MPCs to meet stringent performance targets while reducing the component count and enhancing system integration.

In Section 5, a comparative study is presented between the proposed MPCs and conventional solutions based on multiple interconnected two-port converters. Under mission profiles emulating renewable energy generation and storage, the MPCs consistently outperformed their counterparts, particularly in terms of system-level efficiency and compactness.

Finally, the report details the refinement and validation of a non-linear control strategy originally proposed in D3.1 [1] for the Y-converter topology in Section 6. The enhanced control approach has been extended and adapted for the broader class of MPCs introduced in this work. Its effectiveness is demonstrated through improved transient response, robustness against parameter variations, and overall control performance under varied operating conditions.

#### 2 Introduction

### 2.1 Background and Motivations for Multiport Converters

The urgency of the climate crisis, coupled with the European Union's strategic goal of achieving climate neutrality through net-zero greenhouse gas emissions by 2050, is accelerating the deployment of power converter-interfaced devices within electric power systems. This growing reliance on power electronics, particularly for integrating renewable energy sources (RESs) and energy storage systems (ESSs) into distribution networks (DNs), introduces new operational challenges that demand innovative converter architectures and control strategies to ensure both efficiency and grid reliability [2].

Traditional two-port power converters are often underutilized, especially in scenarios where their controllability is poorly aligned with the variable and often unpredictable nature of demand profiles. This is particularly critical on radial feeders, which are susceptible to significant voltage deviations under generation-demand mismatches [3]. To address this issue, the concept of enhanced soft-open-points (ESOPs) has emerged. These devices interconnect adjacent radial feeders and coordinate with nearby RESs or ESSs, thereby enabling grid-support functionalities such as peak shaving and facilitating greater penetration of low-carbon energy sources [4, 5].

Simultaneously, the proliferation of dc-based systems—such as ESSs and electric vehicle (EV) chargers—has led to an increased number of conversion stages, which adversely impacts system cost, volume, and efficiency. Nevertheless, the widespread availability of energy sources and sinks opens up opportunities for local energy aggregation and sharing. In high converter-density environments, such as residential or commercial buildings, there is significant potential for more streamlined energy integration, resulting in improved overall energy utilization.

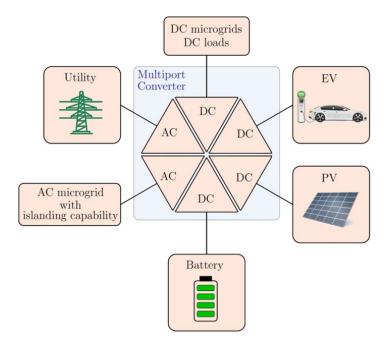

Multiport power converters (MPCs), shown in Fig. 1, offer a promising solution by consolidating multiple energy interfaces—ac and dc—into a single, unified conversion platform [6]. With high controllability and flexibility, MPCs enable efficient energy exchange among various ports, while meeting local constraints such as voltage quality and power balancing. Their inherent capability to reduce the number of required conversion stages relative to conventional multi-terminal ac or dc solutions positions them as attractive candidates for achieving higher power density and cost-effectiveness in modern distribution networks [7].

MPCs are highly versatile, offering configurable port characteristics (ac or dc) and scalable port count, which makes them ideal for acting as centralized energy hubs. These hubs can seamlessly connect multiple feeders, substations, and distributed energy resources. Compared to systems composed of several dedicated two-port converters, MPCs reduce the overall footprint, cost, and complexity, while delivering enhanced power density and

Figure 1: Representation of a Multiport converter interfacing various sources, loads and storages.

integration flexibility.

Another notable advantage of MPCs is their advanced control, communication, and computational capabilities. These features enable decentralized operation, allowing local decision-making without relying solely on centralized grid management. This distributed intelligence fosters faster, more coordinated responses to dynamic grid events, thereby improving resilience and stability [8,9].

On a broader level, MPCs are capable of performing localized grid-support functions—such as voltage regulation, frequency support, and continuity of service—while also contributing to system-wide objectives like efficiency optimization, load balancing, and congestion management. Their flexibility enables them to act as both local controllers and system-level optimizers [10]. Furthermore, future advancements in MPC control will leverage adaptive, data-driven algorithms capable of evolving in response to real-time grid conditions. These adaptive strategies will enhance security, power quality, and dynamic robustness.

The primary objective of WP3 is to investigate and facilitate the deployment of MPCs in low-voltage (LV) distribution networks, addressing both household and broader distribution-level scenarios. Key research directions include the development of compact, high-efficiency circuit topologies capable of interfacing multiple dc ports with single-phase or three-phase ac grids. This will reduce the number of conversion stages, minimize passive component size, and improve overall converter power density.

In parallel, WP3 addresses key control and modulation challenges, including the real-

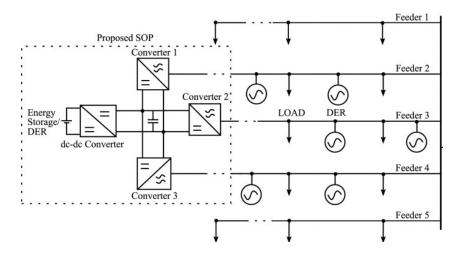

Figure 2: Multiport converter for distribution level scenario.

ization of Zero-Voltage Switching (ZVS) across varying operating conditions. Advanced control methods—such as oversampling techniques and digital hysteresis modulation—will be employed to enhance current and voltage regulation, while preserving passivity and ensuring high control bandwidth across all ports. These innovations are essential to mitigate dynamic instabilities and oscillatory behavior in increasingly complex and flexible future grids.

### 2.2 Scope of WP3 Research Activities

In distribution level scenario where DNs have a significant penetration of renewable sources such as solar PV and wind power plants, along with various industrial loads, electric vehicle charging stations, and energy storage units, power electronics play a vital role. They facilitate the integration of renewables and energy storage systems, optimize the use of the distribution network, and enable the connection of various loads at different voltage levels, both AC and DC as presented in Fig. 2. Several power-electronic solutions have been discussed in the literature for enhancing capacity, improving flexibility, and enhancing controllability in distribution grids. These solutions include ESOP, smart transformers, and multiport converters. Additionally, there is a growing interest in introducing multiport converters in residential areas to accommodate future connections of EVs and distributed renewable generation. For example, a multiport converter has the capability to interconnect two low-voltage (LV) lines in a region to improve the balance of loads, voltages, and renewable capacity.

For distribution-level MPCs, back-to-back voltage source converters (VSCs) have demonstrated superior performance at high power levels and have been widely reported in various industrial projects. Therefore, the topology evaluation of distribution-level MPCs is considered well-covered in the literature [11, 12]. Additionally, as shown for two-port VSCs,

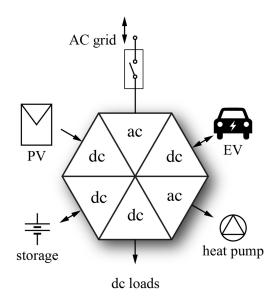

Figure 3: Multiport converter for residential level scenario.

three-level and multi-level VSCs can potentially improve performance compared to two-level VSCs, and these findings can be readily extended to back-to-back VSCs [13,14].

In household/residential settings, MPCs can play a pivotal role in linking local RESs and ESSs with the broader distribution grid as displayed in Fig. 3. Additionally, multiple ports of the converter can be designed to support local energy storage systems and electric vehicles. Implementing MPCs in household installations offers substantial advantages, including enhanced system efficiency and reduced integration costs for renewable energy, EVs, and energy storage compared to traditional methods. This approach not only optimizes energy management at the household level but also contributes to the overall stability and efficiency of the distribution network, paving the way for more resilient and cost-effective energy solutions.

For household/residential scenario, The primary technical and scientific objectives are threefold: First, it aims to provide a detailed assessment and evaluation of MPCs in low-voltage (LV) applications compared to multiple converters. This will involve a comprehensive analysis of losses, volume, and optimization of semiconductor devices and passive elements, considering factors such as switching frequency and wide bandgap device technologies. Second, the project seeks to propose novel MPC topologies to overcome existing limitations, such as reliance on DC-link or magnetic coupling, restrictions on power exchange, and the presence of circulating currents. These novel topologies will aim for single-stage power conversion, enhanced efficiency, power density, and bidirectional power flow at all ports. Third, the project will focus on ensuring reliable and high-performance control of MPCs through advanced controllers, oversampling, and digital hysteresis modulation,

addressing dynamic interactions and minimizing disturbances with other power electronics converters in distribution grids.

### 2.3 Interrelations with WP3 Previous Deliverable (D3.1)

Deliverable 3.1 [1] of the iPLUG project provided the initial foundations for WP3, identifying the core challenges associated with soft open point (SOP) converters in LV networks, and introducing a passivity-oriented control framework to ensure robust stability. Key outcomes included the proposal of novel single-stage, non-isolated multiport converter topologies for residential applications and the demonstration of improved dynamic performance via a non-linear control law applied to the Y-converter.

Building directly on those results, Deliverable D3.2 shifts focus from topology and control design to hands-on experimental validation. The laboratory prototypes developed here embody the single-stage MPC architectures introduced in D3.1 [1], and are tested under both steady-state and dynamic operating conditions that emulate real-world grid-interfacing and energy-management scenarios.

Furthermore, D3.2 extends the scope of evaluation by incorporating a multi-objective optimization framework, targeting simultaneously high conversion efficiency and elevated power density—two metrics that are critical for compact, cost-effective LV power conversion. Comparative studies against cascaded two-port converter arrangements demonstrate that the MPCs deliver superior system-level efficiency and reduced component count under renewable-generation mission profiles. Finally, the non-linear control strategy first developed for the Y-converter in D3.1 [1] has been refined and generalized to the broader MPC scenario.

### 2.4 Interrelations with Other WPs in the iPlug Project

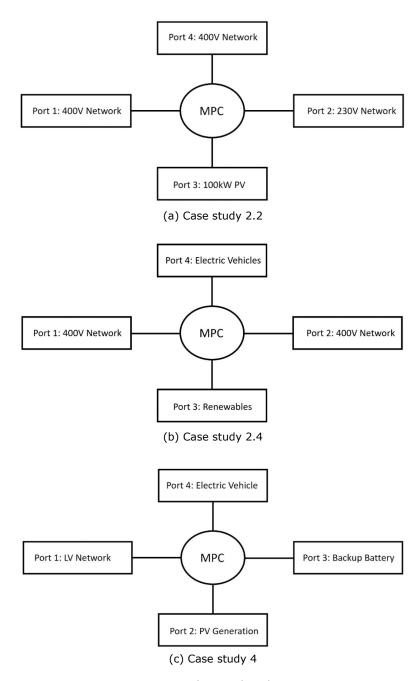

The activities of WP3 are organized to align with the outcomes of WP1, ensuring compliance with grid codes and standards, considering the defined KPIs for evaluating different converters, and adopting the case studies presented in WP1. The following case studies, shown in Fig. 4, have been considered in WP3 activities: Case Study 2.2 for interconnection of LV feeders, Case Study 2.4 for LV residential areas, and Case Study 4 for smart home installations.

Considering the interrelation with WP2, the proposed control techniques for FRT and impedance passivity can be extended to the medium-voltage case studies addressed in WP2. Additionally, the evaluation studies presented in WP3 can provide valuable insights for topology evaluation and ranking in WP2. Moreover, both WP2 and WP3 shared the same approach of rapid prototyping using Imperix modules and controllers for prototype development and experimental verification. For WP4, the proposed converters in WP3 and

Figure 4: WP1 case studies utilized in WP3 activities.

the impedance passivity approach can be utilized in the grid-interaction studies undertaken in WP4.

#### 2.5 Summary of Contributions in This Deliverable

# 2.5.1 Experimental Prototype Development for the Proposed Multiport Converters

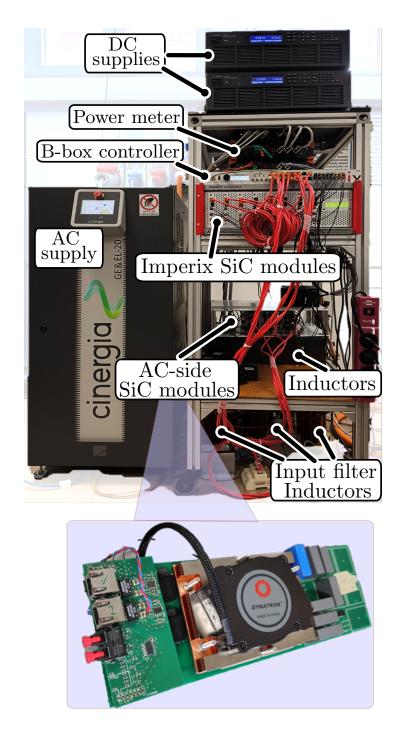

A rapid-prototyping setup is employed to enable flexible experimental testing of the proposed multiport converters under both steady-state and dynamic conditions.

The experimental prototype integrates two distinct types of half-bridge modules, each selected or custom-designed to meet the specific electrical and functional requirements of the respective stages in the multiport converter.

Six commercial Imperix PEB8024 half-bridge power modules are used for the boost stages. These modules incorporate C2M0080120D SiC MOSFETs, providing robust switching performance along with integrated protection features, which are advantageous for rapid development. However, the C2M0080120D devices exhibit a relatively high on-state resistance of  $80\,\mathrm{m}\Omega$ , contributing to elevated conduction losses, particularly under high current operation. Additionally, each Imperix module includes a sizable built-in dc-link capacitor of  $235\,\mathrm{\mu F}$ , which, while beneficial for stabilizing the dc voltage, results in significant reactive power consumption when interfacing with the ac grid.

To meet the specific requirements of the buck stages—especially those connected to the ac grid—three custom-designed half-bridge modules are developed. These modules utilize UF4SC120023K4S SiC MOSFETs, which offer a significantly lower on-state resistance of  $23\,\text{m}\Omega$ , thus reducing conduction losses under high current conditions. Moreover, the custom modules feature a modular and adjustable dc-link capacitance, configurable between  $3.5\,\mu\text{F}$  and  $20\,\mu\text{F}$ , providing greater flexibility and improved compatibility with grid-connected applications.

This deliverable presents a detailed description of the main building blocks of the prototype, including the semiconductor devices, control architecture, power supplies, power measurement instruments, and related hardware components.

# 2.5.2 Experimental Validation of the Proposed Symmetric and Asymmetric Multiport Y-converters

A detailed experimental validation of both the symmetric and asymmetric variants of the proposed multiport Y-converter is presented in this deliverable. The developed hardware prototypes have been extensively tested under a variety of operating scenarios to verify the theoretical analysis, assess dynamic behavior, and evaluate performance metrics such as current sharing, voltage regulation, power conversion efficiency, and grid current quality.

The experimental setup replicates real-world conditions through the integration of bidirectional ac and dc programmable power supplies, real-time control platforms, and precision measurement instruments. Both converters were subjected to steady-state and dynamic load conditions to capture their transient response, stability margins, and their ability to handle power flow in both directions across ports. Emphasis was placed on validating the correct operation during different load distributions among the dc ports and across multiple operating modes, such as charging, discharging, and simultaneous bidirectional power exchange.

Waveforms captured using high-speed oscilloscopes and real-time data acquisition systems confirm that the converters maintain balanced three-phase grid currents with low total harmonic distortion (THD), even during fast transients. In the symmetric configuration, the results demonstrate uniform power distribution and consistent port behavior due to structural uniformity. In contrast, the asymmetric configuration reveals its capability to manage differential power flows efficiently, thanks to its flexible control strategy and hardware asymmetry tailored for application-specific requirements.

The performance of both prototypes was benchmarked in terms of efficiency across a wide range of operating powers. Using calibrated power meters and synchronized current and voltage measurements, efficiency curves were derived and evaluated.

# 2.5.3 Performance Evaluation of Multiport Y-Converters using Renewable Source Mission Profile

To further highlight the potential of MPCs, the design and optimization of converter topologies for interconnecting 400 V dc MGs with the European low-voltage ac grid is conducted. The Y-converter topology is investigated, offering single-stage power conversion and bidirectional buck-boost capability. Two design approaches are evaluated: employing separate two-port Y-converters (2Y) and utilizing a single, integrated multiport Y-converter. A Pareto optimization framework is applied to explore trade-offs between efficiency and power density, based on detailed analysis of component losses, volume, and design constraints. Results show that both approaches achieve high efficiency and power density, with the MPC exhibiting superior average efficiency for dc power transfer by avoiding additional losses introduced by the intermediate ac stage present in the 2Y configuration. These findings demonstrate the strong potential of MPCs as compact and efficient interfaces for future dc MGs integration with the ac grid.

# 2.5.4 Proposing Nonlinear Control of Y-Converters for Grid Integration of 400 V DC Microgrids

A loss-free resistor hysteresis controller is proposed for the Y-converter as an alternative approach to the conventional linear controllers. The motivation for employing loss-free resistor hysteresis controller over traditional linear controllers lies in its ability to significantly enhance the dynamic performance of power converters. Linear controllers, while widely used, often struggle with rapid transient responses and maintaining stability across a wide range of operating conditions due to their inherent reliance on fixed gain settings and limited bandwidth. In contrast, loss-free resistor hysteresis control dynamically adjusts the switching actions based on real-time system conditions, allowing for precise control of current and voltage with minimal delay. This method also improves response times to transient events and maintains stable operation without the need for complex compensation networks. Additionally, hysteresis control inherently adapts to variations in load and supply conditions, providing a robust solution that enhances overall system reliability. The proposed controller is initially proposed for two-port converter and then extended to multiport converter scenario.

#### 2.6 List of Publications

A set of relevant publications has been realized within WP3, as follows:

- M. D. Hernàndez, O. Esquius Mas, M. C. Mañe, E. Prieto Araujo and O. G. Bellmunt, "Fault Ride Through Control of Multiport Converter for Distribution Grids," 2022 IEEE PES Innovative Smart Grid Technologies Conference Europe (ISGT-Europe), Novi Sad, Serbia, 2022, pp. 1-5, doi: 10.1109/ISGT-Europe54678.2022.9960596.

- A. Y. Farag, D. Biadene, P. Mattavelli and T. Younis, "Three-phase Four-wire Bidirectional Y-converter for an Enhanced Interface between the AC Grid and the Unipolar DC Microgrid," 2023 8th IEEE Workshop on the Electronic Grid (eGRID), Karlsruhe, Germany, 2023, pp. 1-6, doi: 10.1109/eGrid58358.2023.10380894.

- R. Cvetanovic, I. Petric, P. Mattavelli and S. Buso, "MIMO Analysis of Port-Coupling Induced Destabilization of Interlinking DC-DC Converters," 2024 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 2024, pp. 2806-2813, doi: 10.1109/APEC48139.2024.10509432.

- K. A. A. Mohammed, P. Mattavelli, T. Caldognetto, D. Biadene and P. Magnone "Analysis of Low Voltage Ride Through Capability in Multiport Converters for Soft-Open Point Applications," ELECTRIMACS 2024, Castello de la Plana, Spain.

- A. Y. Farag, D. Biadene, T. Caldognetto and P. Mattavelli, "Enhancing DC Microgrids Integration with Three-Phase AC Grids Using Multiport Converters," 2024 Power Electronics, Machines and Drives 13th International Conference PEMD 2024, Nottingham, United Kingdom.

- A. Y. Farag, D. Biadene, P. Mattavelli and T. Younis, "Three-Phase Four-Wire Step-Down Modular Converter for an Enhanced Interlinking in Low-Voltage Hybrid AC/DC Microgrids," in IEEE Open Journal of Power Electronics, vol. 5, pp. 634-647, 2024, doi: 10.1109/OJPEL.2024.3394548.

- A. Y. Farag, D. Biadene, T. Caldognetto and P. Mattavelli, "Multiport Y-Converter for Three-Phase AC Grid Integration with DC Systems," 2024 IEEE 15th International Symposium on Power Electronics for Distributed Generation Systems PEDG 2024, Luxembourg, 2024.

- A. Y. Farag, D. Biadene, T. Caldognetto and P. Mattavelli, "Asymmetric Multiport Y-Converter for Three-Phase AC Grid Integration with DC Microgrids," 2024 Energy Conversion Congress & Expo Europe (ECCE Europe).

- R. Cvetanović, I. Z. Petrić, P. Mattavelli and S. Buso, "On the Applicability of SISO and MIMO Impedance-Based Stability Assessment of DC-DC Interlinking Converters," in IEEE Transactions on Power Electronics, vol. 39, no. 9, pp. 10768-10780, Sept. 2024, doi: 10.1109/TPEL.2024.3403236.

- R. Cvetanović, I. Z. Petrić, P. Mattavelli and S. Buso, "All-Port MIMO Admittance Passivity for Robust Stability of DC-DC Interlinking Converters," in IEEE Transactions on Power Electronics, doi: 10.1109/TPEL.2024.3430560.

- A. Y. Farag, D. Biadene, T. Caldognetto and P. Mattavelli, "Single-Stage Non-Isolated Multiport Y-Converter for Interlinking 400 V DC Microgrids With the Three-Phase AC Grid," in IEEE Open Journal of Power Electronics, vol. 5, pp. 1432-1445, 2024, doi: 10.1109/OJPEL.2024.3462773.

- K. A. A. Mohammed, A. Y. Farag, D. Biadene, T. Caldognetto and P. Mattavelli, "Performance Evaluation of Multiport Y-Converters using Renewable Source Mission Profile," IEEE 7th International Conference on DC Microgrids ICDCM 2025 (To be presented).

- M.B. Debbat, A. Y. Farag, P. Mattavelli, JL. Domínguez-García "Nonlinear Control of the Four-Wire Y-Converter for Grid Integration of 400 V DC Microgrids," IEEE 7th International Conference on DC Microgrids ICDCM 2025. (To be presented).

- K. A. A. Mohammed, A. Y. Farag, D. Biadene, T. Caldognetto, P. Magnone and P. Mattavelli, "Isolated Y-Connected Multiport Converter for Interconnecting DC Systems

with the AC Grid," In IEEE Energy Conversion Conference and Expo ECCE-2025. (**To be presented**).

- A. Y. Farag, D. Biadene, T. Caldognetto, P. Magnone and P. Mattavelli, "Modified Discontinuous Modulation for Mitigating Distortions at Phase Clamping in Y-Converter," In IEEE Energy Conversion Conference and Expo ECCE-2025. (To be presented).

- A. Y. Farag, D. Biadene, T. Caldognetto, P. Magnone and P. Mattavelli, "Low-Frequency Voltage-Ripple Minimization of Asymmetric Multiport Y-Converter," In IEEE Transactions on Power Electronics. (under review).

- M. Domínguez-Hernández, M. Cheah-Mañé, R. Griñó, and O. Gomis-Bellmunt, "Centralized DC Voltage Control for a Multiport Converter in Distribution Grids," International Journal of Electrical Power & Energy Systems. (under review)

- A. Y. Farag, K. A. A. Mohammed, D. Biadene, T. Caldognetto, P. Magnone and P. Mattavelli, "Pareto-Driven Assessment of PWM-Based Performance Enhancements in Multiport Y-Converter," In IEEE CONFERENCE ON POWER ELECTRONICS AND RENEWABLE ENERGY CPERE-2025. (under review).

## 3 Experimental Verification of the Multiport Y-Converter

This section briefly reviews the fundamental operation and analysis of the proposed symmetric multiport Y-converter, with the primary focus on prototype development and experimental validation. A more comprehensive analysis and evaluation of the multiport Y-converter can be found in D3.1 [1].

#### 3.1 Brief Analysis and Background

#### 3.1.1 Derivation and Operation Principle

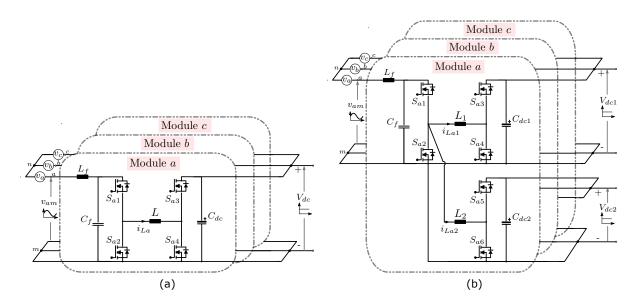

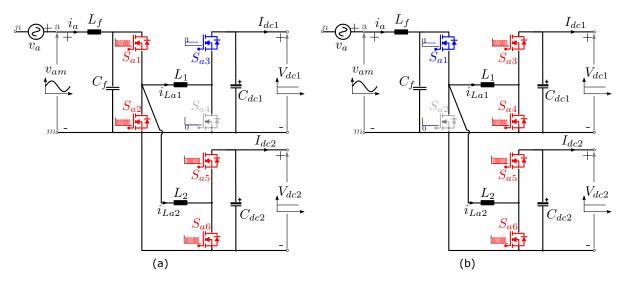

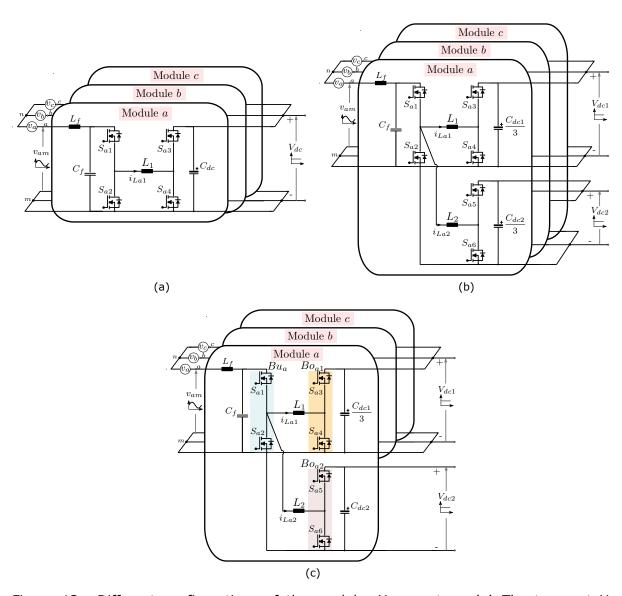

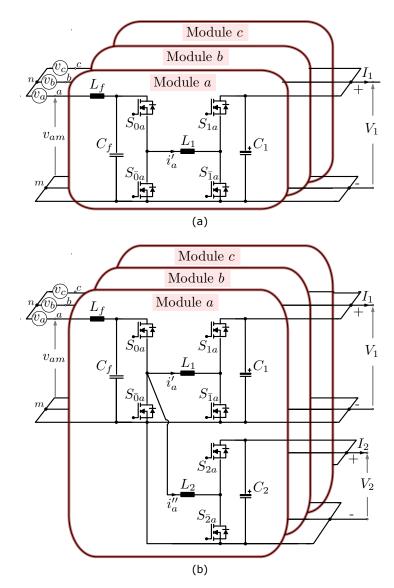

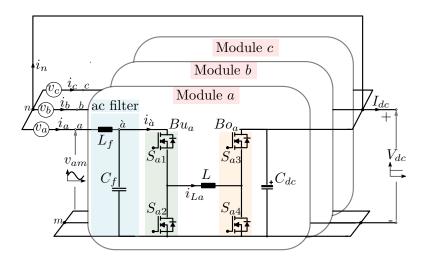

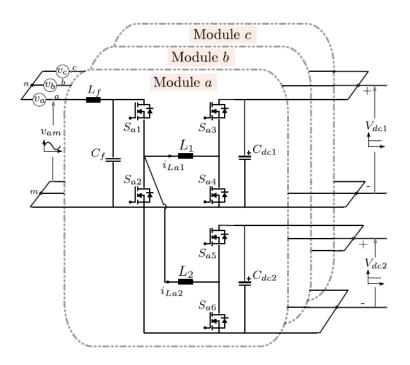

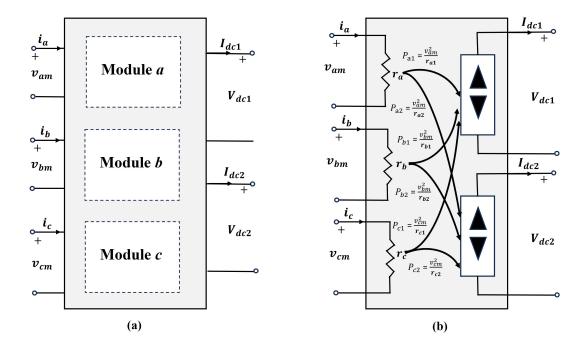

The proposed multiport converter topology is derived from the Y-converter, as depicted in Fig. 5a, transforming it from a two-port configuration into a multi-port structure capable of connecting multiple dc ports to a three-phase ac grid, as illustrated in Fig. 5b. Initially, the two-port Y-converter comprised three four-switch buck-boost modules [15,16]. Alternatively, in the proposed converter, each module is expanded into a six-switch dc-dc converter. Considering the structure of a three-port converter, the upgraded design includes a shared buck half-bridge and two boost half-bridges, establishing connections to the dc ports. Notably, the configuration is potentially adaptable to additional dc ports by incorporating one boost converter into each module for every extra dc port, thus maintaining scalability.

Figure 5: A schematic of two-port and multiport Y-converters in a modular form: (a) Two-port Y-converter; (b) The symmetric Multiport Y-converter.

Similar to the two-port Y-converter, the three modified modules are interconnected at a central point denoted as m, serving as the neutral point for the Y-connection of the modules. Since each module functions as a dc-dc converter, maintaining a non-negative voltage on the ac side of the module  $(v_{\{a,b,c\}m} \geq 0\,\text{V})$  is crucial. To achieve this, an offset voltage is

required between the grid's neutral point n and m. A constant offset voltage ( $V_{off}$ ) is then applied, which must exceed the peak value of the ac grid phase voltage ( $\hat{V}_m$ ). The ac-side voltages  $v_{am}$ ,  $v_{bm}$ , and  $v_{cm}$  can be expressed as follows:

$$v_{xm}(t) = v_x(t) + V_{off} = \hat{V}_m \sin(\omega t + \theta_x) + V_{off}$$

(1)

where  $v_x$ , with x=(a,b,c), represents the ac grid phase voltages,  $\omega$  denotes the ac grid frequency in rad/s, and  $\theta_x$  signifies the respective phase angles of  $v_x$ .

Since  $V_{off}$  also represents the common-mode voltage (CMV) of the converter, the fixed CMV is an additional advantage of the proposed topology. While CMV can pose a threat to overall system performance by inducing leakage current through parasitic capacitances to ground and causing electromagnetic interference (EMI) in the high-frequency range [17], the fixed CMV in the proposed topology minimizes these issues as the leakage current flowing through parasitic capacitances is significantly reduced.

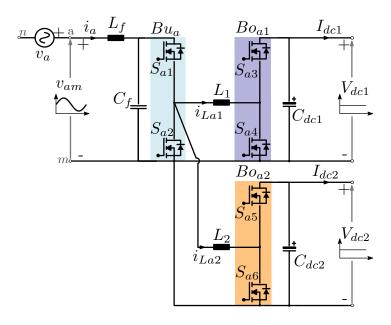

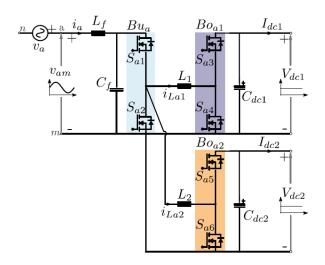

The analysis of the converter is presented by considering a single module (module a), as depicted in Fig. 6, and it similarly applies to the other modules as well. This module consists of the two inductors  $L_1$  and  $L_2$  along with three half-bridges: one on the ac side, labeled as  $Bu_a$ , and the others on the dc sides, labeled as  $Bo_{a1}$  and  $Bo_{a2}$ . Although the main focus of this article is on interfacing 400 V dc systems, the subsequent analysis is generalized for arbitrary values of  $V_{dc1}$  and  $V_{dc2}$ . Additionally, it is assumed that at least one of the dc ports' voltage is lower than the peak of the ac side voltage ( $\hat{V}_m + V_{off}$ ), and  $V_{dc1}$  is lower than  $V_{dc2}$ . Based on these assumptions, the  $Bu_a$  and  $Bo_{a1}$  half-bridges are under control, ensuring that only one of them is modulated at any given moment, while the other remains clamped based on the values of  $v_{am}$  and  $V_{dc1}$ , whereas  $Bo_{a2}$  will be modulated continuously.

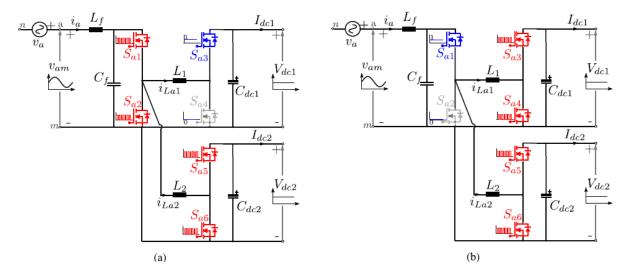

#### 3.1.2 Analysis and Fundamental Relations

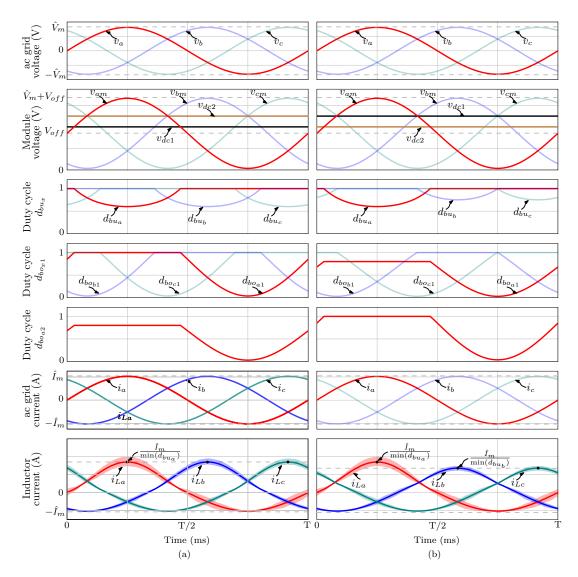

**3.1.2.1 Buck Mode** When  $v_{am}$  exceeds  $V_{dc1}$ , module a operates in buck mode. In this mode, the  $Bu_a$  half-bridge switches, while the  $Bo_{a1}$  half-bridge is clamped with  $S_{a3}$  on and  $S_{a4}$  off, as illustrated in Fig. 7a. Simultaneously, the  $Bo_{a2}$  half-bridge operates with a fixed duty cycle, depending on the ratio between  $V_{dc1}$  and  $V_{dc2}$ . The duty cycles of  $S_{a1}$  and  $S_{a5}$ , denoted as  $d_{Bu_a}$  and  $d_{Bo_{a2}}$ , respectively, can be calculated using the following equations:

$$d_{Bu_a}(t) = \frac{V_{dc1}}{v_{am}(t)} = \frac{V_{dc1}}{\hat{V}_m \sin(\omega t) + V_{off}}$$

(2)

$$d_{Bo_{a2}} = \frac{V_{dc1}}{V_{dc2}} \tag{3}$$

The ac grid current of phase a, denoted as  $i_a$ , is assumed to be pure sinusoidal and in

Figure 6: Module a of the proposed converter.

Figure 7: Operation modes of one module of the proposed converter: (a) Buck mode when  $v_{am}>V_{dc1}$ ; (b) Boost mode when  $v_{am}< V_{dc1}$

phase with its corresponding phase voltage  $\emph{v}_\emph{a}$  and then can be calculated as follows:

$$\begin{split} i_a(t) &= \hat{I}_m \sin(\omega t) = (\hat{I}_{m1} + \hat{I}_{m2}) \sin(\omega t) \\ &= \left(\frac{2P_{dc1}}{3\hat{V}_m} + \frac{2P_{dc2}}{3\hat{V}_m}\right) \sin(\omega t) \end{split} \tag{4}$$

where  $P_{dc1}$  and  $P_{dc2}$  represent the power delivered to dc ports 1 and 2, respectively, while  $\hat{I}_m$  denotes the peak phase current. Additionally,  $\hat{I}_{m1}$  and  $\hat{I}_{m2}$  signify the equivalent reference peak phase current solely due to the power of dc MG#1 and #2, respectively.

The summation of average inductor currents (i.e.,  $i_{La1,av} + i_{La2,av}$ ), denoted as  $i_{La,av}$ , can be derived by applying Kirchhoff's current law (KCL) at the ac input of the module, as follows:

$$i_{La,av}(t) = i_{La1,av}(t) + i_{La2,av}(t) = \frac{i_a(t) - i_{Cf,a}(t)}{d_{Bu_a}(t)}$$

(5)

where  $i_{Cf,a}$  represents the current through the input capacitor  $C_f$ . By neglecting  $i_{Cf,a}$ , the equation can be simplified as follows:

$$i_{La,av}(t) = \frac{i_a(t)}{d_{Bu_a}(t)} = \frac{\hat{I}_m \sin(\omega t)}{d_{Bu_a}(t)}$$

$$\tag{6}$$

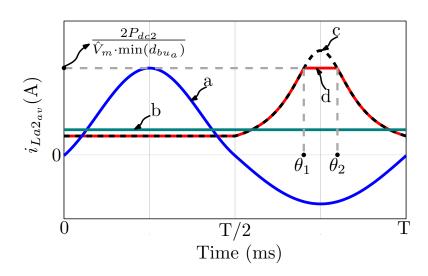

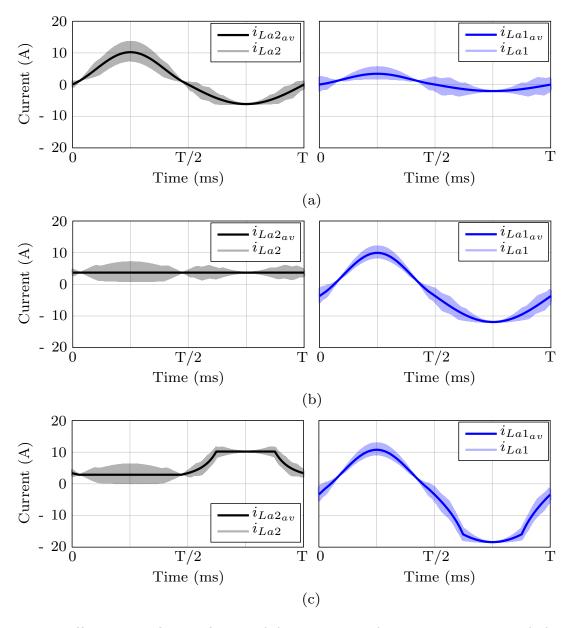

Using (4) and (6) ,  $i_{la1,av}$  and  $i_{la2,av}$  can be determined as follows:

$$i_{La1,av}(t) = \frac{\hat{I}_{m1}\sin(\omega t)}{d_{Bu_a}}$$

$$i_{La2,av}(t) = \frac{\hat{I}_{m2}\sin(\omega t)}{d_{Bu_a}}$$

(7)

**3.1.2.2 Boost Mode** The second mode of operation occurs when  $v_{am}$  falls below  $V_{dc1}$ . In this mode, module a operates in boost mode. In this mode, the  $Bo_{a1}$  half-bridge switches, while the  $Bu_a$  half-bridge is clamped with  $S_{a1}$  on and  $S_{a2}$  off, as depicted in Fig. 7b. Simultaneously, the  $Bo_{a2}$  half-bridge operates with a time-varying duty cycle. The duty cycles of  $S_{a3}$ , denoted as  $d_{Bo_{a1}}$ , and  $d_{Bo_{a2}}$  can be calculated using the following equations:

$$d_{Bo_{a1}}(t) = \frac{v_{am}(t)}{V_{dc1}} \tag{8}$$

$$d_{Bo_{a2}}(t) = \frac{v_{am}(t)}{V_{dc2}} \tag{9}$$

Using (7) and given that  $d_{Bu_a}=1$  in this mode,  $i_{La1,av}$  and  $i_{La2,av}$  can be determined as:

$$i_{La1,av}(t) = \hat{I}_{m1}\sin(\omega t)$$

$$i_{La2,av}(t) = \hat{I}_{m2}\sin(\omega t)$$

(10)

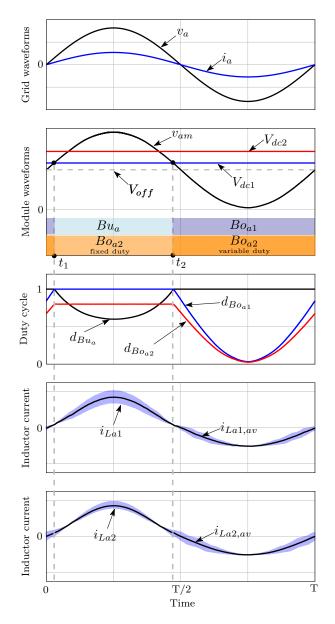

Figure 8: Key waveforms of module a of the proposed converter.

The key waveforms for module a of the proposed converter are plotted in Fig. 8. Additionally, the basic characteristic equations of the proposed converter are summarized in Table 1. These equations are applicable to any values of  $V_{dc1}$  and  $V_{dc2}$ , including the scenario presented in the analysis (where  $V_{dc1}$  is lower than  $V_{dc2}$ ) and also when  $V_{dc1}$  is higher than  $V_{dc2}$ .

### 3.2 Description of the Experimental prototype

This section provides a detailed overview of the experimental prototype used to validate both the symmetric and asymmetric multiport Y-converters, highlighting the main components along with their key features and specifications. Fig. 9 shows the rapid-prototyping

Table 1: Summary of the basic equations of the proposed converter.

| <b>Parameter</b> | Equation                                                   | <b>Parameter</b> | Equation                                        |

|------------------|------------------------------------------------------------|------------------|-------------------------------------------------|

| $v_x$            | $\hat{V}_m \sin(\omega t + 	heta_x)$                       | $v_{xm}$         | $v_x + V_{off}$                                 |

| $d_{Bu_x}$       | $\frac{min(v_{xm}, V_{dc1}, V_{dc2})}{v_{xm}}$             | $d_{Bo_{x1}}$    | $\frac{min(v_{xm}, V_{dc1}, V_{dc2})}{V_{dc1}}$ |

| $d_{Bo_{x2}}$    | $rac{min(v_{xm}, V_{dc1}, V_{dc2})}{V_{dc2}}$             | $i_{Lx,av}$      | $rac{\hat{I}_m  sin(\omega t + 	heta_x)}{}$    |

| $i_{Lx1,av}$     | $rac{2P_{dc1}\sin(\omega t+	heta_x)}{3\hat{V}_md_{Bu_x}}$ | $i_{Lx2,av}$     | $\frac{d_{Bu_x}}{3\hat{V}_m d_{Bu_x}}$          |

setup employed to facilitate flexible experimental testing of the proposed converters under both steady-state and dynamic conditions. While this approach enables quick verification of functionality and control performance, it does not yield optimized efficiency or power density; those optimization efforts are discussed later in this deliverable.

#### 3.2.1 Semiconductor devices

The experimental prototype integrates two different types of half-bridge modules, each selected and designed to optimally fulfill the requirements of the respective stages in the multiport converter. The prototype consists of six commercial Imperix PEB8024 half-bridge power modules are employed. These modules utilize C2M0080120D SiC MOSFETs and the modules offer reliable switching performance and integrated protection features, making them well-suited for rapid prototyping and development. However, they come with certain limitations: the MOSFETs exhibit a relatively high on-state resistance of  $80\,\mathrm{m}\Omega$ , leading to increased conduction losses, particularly under high current conditions. Furthermore, each module includes a substantial built-in dc-link capacitance of  $235\,\mu\mathrm{F}$ , which, although beneficial for voltage dc voltage stabilization, when connected to ac grid it consumes a high reactive power.

To address the specific demands of the buck stages—particularly those interfacing with the ac grid—three custom half-bridge modules were designed. These modules are built around the UF4SC120023K4S SiC MOSFETs, which feature significantly lower on-state resistance ( $23\,\mathrm{m}\Omega$ ). This characteristic is essential to reduce conduction losses during high-current operation, which is more critical on the ac side. In contrast to the Imperix modules, the custom boards incorporate a modular and adjustable dc-link capacitance, ranging from  $3.5\,\mathrm{\mu F}$  to  $20\,\mathrm{\mu F}$ .

In addition to power stage considerations, both module types are equipped with suitable gate-driving and sensing circuitry. Isolated gate drivers with high dV/dt immunity ensure robust switching performance, while onboard sensing elements provide accurate current and voltage measurements for closed-loop control. The gate drivers are designed with adjustable dead-time settings, and each half bridge integrates current sensing of the half-

Figure 9: Picture of the experimental prototype of the proposed converter.

bridge's mid-point current and a voltage sensing for dc-link monitoring.

Overall, the combination of commercial modules for the boost stages and customized designs for the buck stages enables a flexible and efficient hardware platform. This hybrid approach supports comprehensive experimental validation of the proposed symmetric and asymmetric multiport Y-converters, capturing both steady-state and dynamic behavior under realistic grid-connected scenarios. It also establishes a foundation for future refinement toward a more power-dense and cost-optimized converter implementation.

#### 3.2.2 Control architecture

The control architecture of the experimental prototype leverages two Imperix B-Box rapid control prototyping (RCP) controllers configured in a master-slave arrangement for the symmetric multiport Y-converter while a single B-Box is used for the asymmetric topology. This setup facilitates the management of complex multiport converter operations by distributing control tasks across the two units. The master controller oversees the primary control algorithms and coordinates the overall system behavior, while the slave controller handles auxiliary functions and specific control loops, ensuring synchronized operation across all converter ports.

Programming of the B-Box controllers is accomplished through MATLAB/Simulink, utilizing Imperix's Automated Code Generation (ACG) software development kit (SDK). This integration allows for seamless transition from simulation to real-time implementation, enabling rapid prototyping and iterative development of control strategies. The Simulink environment provides a user-friendly interface for designing control algorithms, which are then automatically converted into executable code for the B-Box controllers.

Real-time monitoring and debugging are facilitated by Imperix Cockpit, a comprehensive software tool designed for power electronics applications. Cockpit offers a suite of features including real-time visualization of control variables, parameter tuning without the need for code recompilation, and data logging capabilities. The software supports the creation of custom dashboards through its GUI Builder, allowing users to tailor the monitoring interface to specific application needs. Additionally, Cockpit enables the scheduling of transient events and the application of test scenarios, providing a robust platform for system validation and performance assessment.

#### 3.2.3 Magnetic components

$330\,\mu\text{H}$  inductors are employed for the main inductors  $L_1$  and  $L_2$ , utilizing Fluxsan FS-301026-2 magnetic cores. Each inductor is wound with copper wire, resulting in a total resistance of  $21\,\text{m}\Omega$ . Additionally, the grid-side filter inductor  $L_f$  is implemented using  $1.2\,\text{mH}$  inductors, constructed with ferrite cores and copper windings with a total resistance

of  $30\,\mathrm{m}\Omega$ . All inductors are designed to support a saturation current of  $40\,\mathrm{A}$ .

#### 3.2.4 Power supplies