### **iPLUG**

#### **Deliverable D2.2**

### Comparison and experimental validation of MV multiport converter

### **Document information**

Deliverable nr D2.2

Deliverable Name Comparison and experimental validation of MV multiport converter

Version 01

Release date 13/06/2025

Dissemination level Public

Status Submitted

Authors Mebtu Beza (CTH)

Sam Harrison and Agusti Egea Alvarez (UoS)

Ahmed A. Ibrahim and Ahmed Yahia Farag Abdelfattah (UNIPD)

Martí Domínguez, Marc Cheah Mañe and Oriol Gomis-Bellmunt (UPC)

# **Document history:**

| Version | Date of issue | Content and changes                               | Edited by                  |

|---------|---------------|---------------------------------------------------|----------------------------|

| 01      | 13/05/2025    | First draft                                       | CTH, UoS, UPC and UNIPD    |

| 01      | 26/05/2025    | Revision                                          | Typhoon HIL                |

| 02      | 10/06/2025    | Final formatting and review of the whole document | CTH, UoS, UPC and<br>UNIPD |

|         |               |                                                   |                            |

# Peer reviewed by:

| Partner | Reviewer                          |

|---------|-----------------------------------|

| UNIPD   | Ahmed Yahia Farag<br>Abdelfattah  |

| ТҮРН    | Sergio Costa and<br>Milos Miletic |

## **Deliverable beneficiaries:**

| WP / task         |

|-------------------|

| WP2 / T2.3 & T2.4 |

# **Table of contents**

| 1 | Exe  | ecutive summary                                                        | 15 |

|---|------|------------------------------------------------------------------------|----|

| 2 | Int  | roduction                                                              | 16 |

| 3 | Ide  | ntification of a topology for medium-voltage laboratory verification   | 18 |

|   | 3.1  | Application Specifications                                             | 18 |

|   | 3.2  | Exploration of Feasible Conversion Approaches                          | 19 |

|   |      | 3.2.1 Partially-isolated Topologies                                    | 20 |

|   |      | 3.2.2 Isolated Topologies                                              | 24 |

|   | 3.3  | Comparison of Winning Topologies                                       | 26 |

|   |      | 3.3.1 Number of Components                                             | 27 |

|   |      | 3.3.2 Qualitative Scoring of Topology Characteristics                  | 36 |

|   | 3.4  | Discussion and Conclusions                                             | 38 |

| 4 | Eva  | luation and Model-Free Optimization of Isolated DC-DC Triple-Active-   | -  |

|   | Brid | dge Converters for MV Multiport Converter Applications                 | 40 |

|   | 4.1  | Introduction                                                           | 40 |

|   | 4.2  | Optimal Modulation of TAB Converters                                   | 42 |

|   |      | 4.2.1 Optimizing MPSM for Minimum rms Current                          | 42 |

|   |      | 4.2.2 Optimizing MPSM for Enhanced ZVS and Reduced rms Current $\dots$ | 43 |

|   | 4.3  | Online Model-Free Optimization of TAB                                  | 46 |

|   | 4.4  | Simulation Results                                                     | 47 |

|   | 4.5  | Experimental results                                                   | 49 |

|   | 4.6  | Conclusion                                                             | 51 |

| 5 | Swi  | itching models and CHIL tests in non-isolated MV-MPC                   | 55 |

|   | 5.1  | Modulation                                                             | 55 |

|   | 5.2  | Outer loop comparison                                                  | 56 |

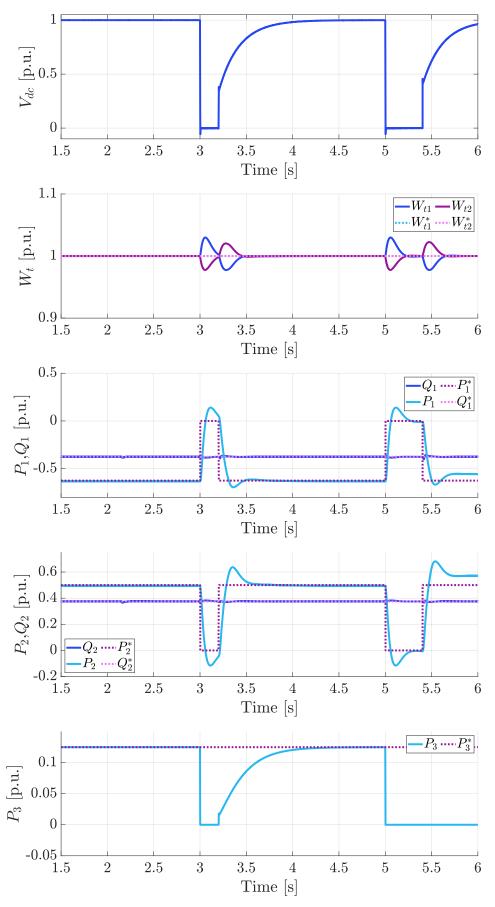

|   |      | 5.2.1 Scenario 1: Classical Control                                    | 58 |

|   |      | 5.2.2 Scenario 2: Crossed Control                                      | 58 |

|   |      | 5.2.3 Scenario 3: Combined Control                                     | 62 |

|   | 5.3  | Control Hardware in the Loop Validation                                | 62 |

|   |      | 5.3.1 Combined Control                                                 | 64 |

|   | 5.4  | Conclusion                                                             | 67 |

| 6 | Exp  | perimental validation of the selected MPC topology                     | 68 |

|   | 6.1  | Description of the lab prototype                                       | 68 |

|   | 6.2  | Main controllers of the lab prototype                                  | 68 |

| 7 | Conclusions                                    | 99 |

|---|------------------------------------------------|----|

|   | 6.4 Conclusion                                 | 98 |

|   | 6.3.2 Impact of abnormal operation conditions  | 80 |

|   | 6.3.1 Dynamic performance in normal conditions | 73 |

|   | 6.3 Operation of the multiport converter       | 72 |

|   | 6.2.3 DC-port load/source                      | 72 |

|   | 6.2.2 Two-level converter - AC port 1          | 72 |

|   | 6.2.1 Multilevel converter - AC port 2         | 69 |

## **List of Acronyms**

AC Alternating current

CHB Cascaded H(full)-bridge

CHIL Control Hardware in the loop

DAB Dual-active bridge

DC Direct current

DN Distribution network

EMI Electromagnetic Interference

ESOP Enhanced soft-open point

ESS Energy storage system

FB Full(H) bridge

FRT Fault ride through

GaN Gallium Nitride

HfB Half bridge

HFT High-Frequency Transformer

iM2DC Isolated multilevel modular dc converter

IMPC Isolated Multi-Port Converter

ISOP isolated soft-open-point

L/HF Low/High frequency

L/MV Low/Meduim voltage)

MAB Multi-acitve bridge

MD-RCC Multi-Dimensional Ripple Correlation Control

ML Multilevel

MMC Modular multilevel converter

MPC Multiport converter

MPSM Multi-Phase Shift Modulation MPSM Multi-Phase Shift Modulation

NLM Nearest Level Modulation

QAB Quadruple Active Bridge

PI Proportional integral

PSC Phase Shifted Carrier

PSM Phase Shift Modulation

PWM Pulse width modulation

RCC Ripple Correlation Control

SiC Silicon Carbide

SM Sub module

SOP Soft open point

STATCOM Static synchronous compensator

SVPWM Space Vector Pulse width modulation

TAB Triple-active bridge

VSC Voltage source converter ZVS Zero Voltage Switching

## **List of Nomenclatures**

$C_{\rm DC}$  DC capacitor

$C_{\text{eq}}$  Equivalent capacitor

$C_{SM}$  Submodule capacitor

$C_{x}$  Number of components in configuration x

$F_s$  Switching frequency

$f_{Sw}$  Switching frequency

$i_{DC}$  DC current

$i_1^{j}$  Lower arm current

*i*<sub>pr</sub> Prioritized current

$i_{ad}$  Grid current

$i_{\rm u}^{\rm j}$  Upper arm current

L Inductance

$L_{\rm f}$  Filter inductor

m MMC AC/DC voltage modulation ratio

$M_x$  Number of DC/DC modules in configuration x

$N_{\rm arm}$  Submodules per arm

$N_x$  Number of AC/DC SMs in configuration x

P Active power

Q Reactive power

R Resistance

S Converter power

t Time

T.C. Transformer cores

T.W. Transformer windings

V PCC voltage

$V_{Cl}^{j}$  Applied lower arm voltage

$V_{\text{conv}}$  Converter voltage

$V_{Cu}^{J}$  Applied upper arm voltage

$V_{\rm dc}$  DC port voltage

$V_1^{\rm j}$  Lower arm voltage

$V_{\rm SM}$  SM capacitor voltage

V<sub>sum</sub> Additive voltage

$V_{\rm u}^{\rm j}$  Upper arm voltage

W Energy

X Reactance

$\alpha_i$  Weighting parameter

# **List of Figures**

| 1  | Enhanced soft open point application diagram                                                                   | 18 |

|----|----------------------------------------------------------------------------------------------------------------|----|

| 2  | Dual-active bridge topology                                                                                    | 21 |

| 3  | Isolated modular multilevel DC converter topology. Figure from [7]                                             | 22 |

| 4  | Input-series Output-parallel converter topology. Figure from [19]                                              | 23 |

| 5  | Partially-isolated topology winner: Back-to-back full-bridge modular multilevel                                |    |

|    | converter with input-series output-parallel dual-active bridge topology                                        | 24 |

| 6  | Triple/multi-active bridge module. Figure from [14]                                                            | 25 |

| 7  | Multi multi-active bridge topology with intermediate AC stage. Topology de-                                    |    |

|    | rived from [21]                                                                                                | 26 |

| 8  | Multi multi-active bridge topology with intermediate DC stage. Topology de-                                    |    |

|    | rived from [21]                                                                                                | 27 |

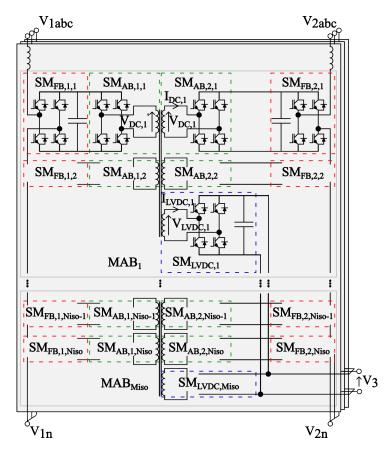

| 9  | Isolated topology winner: Cascaded H-bridge with multi multi-active bridge                                     | 28 |

| 10 | Comparison of component numbers for Case 1: 2x 20 kV AC DN ports and 1x                                        |    |

|    | 400 V DC ESS port                                                                                              | 32 |

| 11 | Comparison of component numbers for Case 2: 2x 5 kV AC DN ports and 1x                                         |    |

|    | 800 V DC ESS port                                                                                              | 35 |

| 12 | Comparison of qualitative feature scoring                                                                      | 38 |

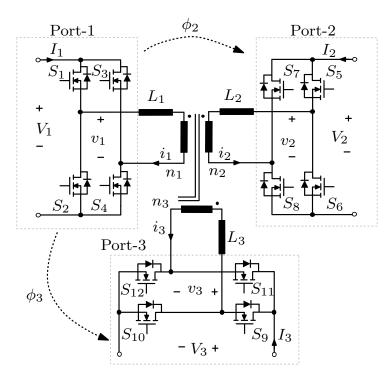

| 13 | TAB converter                                                                                                  | 41 |

| 14 | Switching sequence of TAB modulation schemes: (a) phase-shift modulation                                       |    |

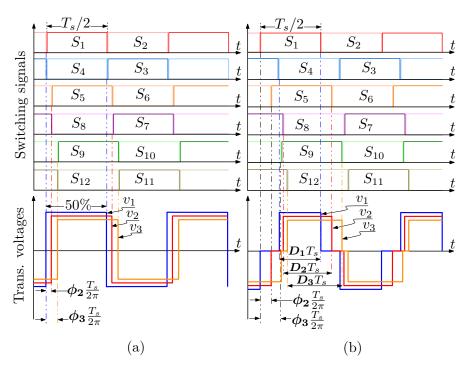

|    | (PSM); (b) multiphase-shift modulation (MPSM)                                                                  | 43 |

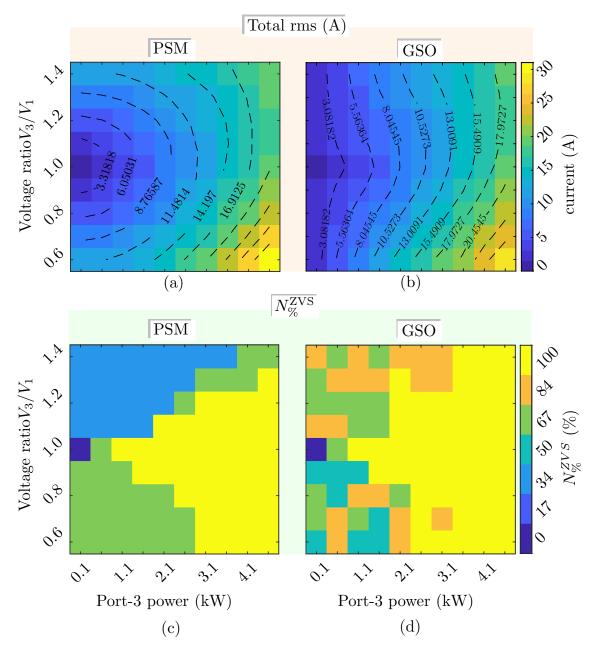

| 15 | Simulation results of TAB; (a)-(b) total rms current for PSM and GSO, respec-                                  |    |

|    | tively; (c)-(d) percentage of devices achieving ZVS ( $N_{\%}^{\text{ZVS}}$ ) for PSM and GSO,                 |    |

|    | respectively. Converter parameters as in Table 5 of Sec. 4.4                                                   | 44 |

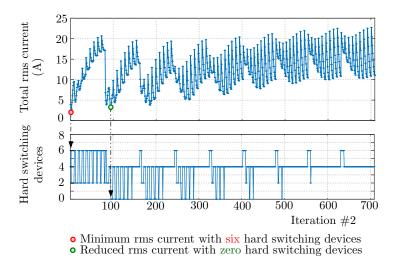

| 16 | Total rms current and the corresponding number of hard switching devices for                                   |    |

|    | each iteration of GSO                                                                                          | 45 |

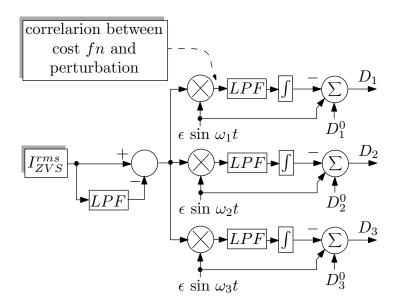

|    | Multi-dimensional ripple correlation search (MD-RCC)                                                           | 46 |

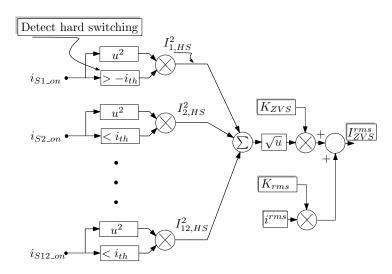

| 18 | Hard switching current detection algorithm of the TAB in Fig. 13; $i_{th}$ calculated                          |    |

|    | with (17)                                                                                                      | 48 |

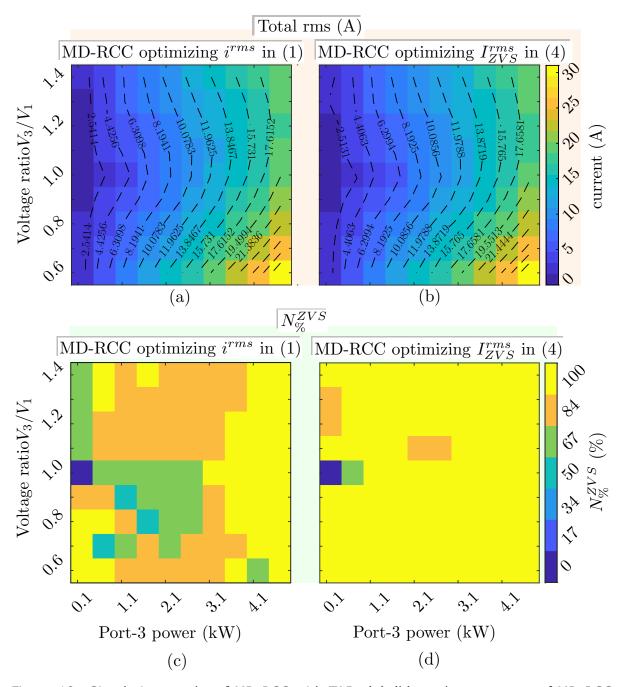

| 19 | Simulation results of MD-RCC with TAB: (a)-(b) total rms current of MD-RCC                                     |    |

|    | optimizing $i^{rms}$ in (16), and $I^{rms}_{ZVS}$ in (19), respectively; (c)-(d) percentage                    |    |

|    | devices achieving ZVS ( $N_{\%}^{\text{ZVS}}$ ) of MD-RCC optimizing $i^{rms}$ in (16), and $I_{ZVS}^{rms}$ in |    |

|    | (19), respectively                                                                                             | 50 |

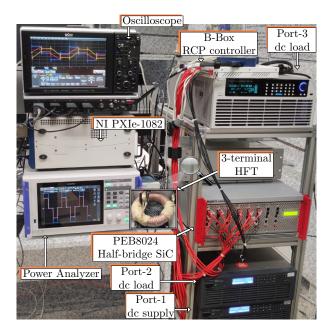

| 20 | TAB experimental prototype                                                                                     | 51 |

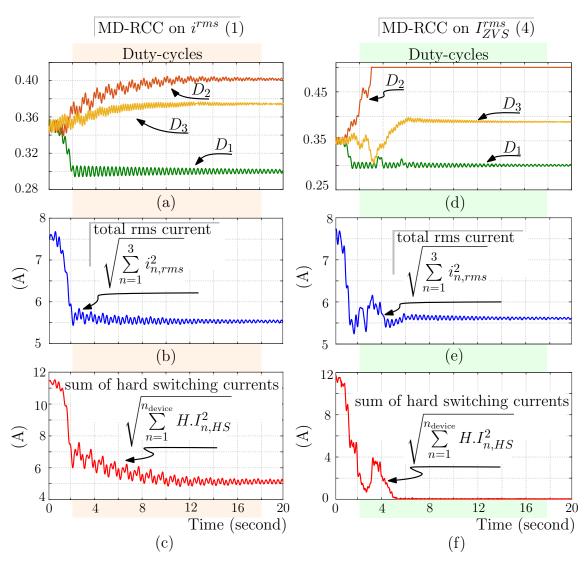

| 21 | (a), (b), and (c) dynamic response of MD-RCC optimizing $i^{rms}$ (16) : (a) duty-   |    |

|----|--------------------------------------------------------------------------------------|----|

|    | cycles; (b) total rms current; (c) sum of hard switching current; (d), (e), and      |    |

|    | (f) dynamic response of MD-RCC optimizing $i_{ZVS}^{rms}$ (19): (d) duty-cycles; (e) |    |

|    | total rms current; (f) sum of hard switching current                                 | 52 |

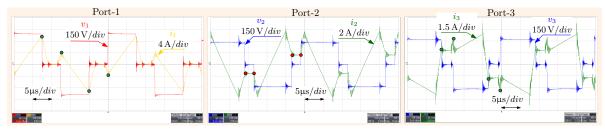

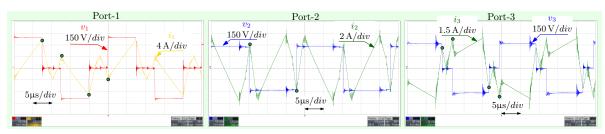

| 22 | Transformer voltage and current steady-state waveforms of the test case in           |    |

|    | Fig. 21: (a) at the initial state; (b) after MD-RCC optimizing $i^{rms}$ (16); after |    |

|    | MD-RCC optimizing $I_{ZVS}^{rms}$ (19)                                               | 53 |

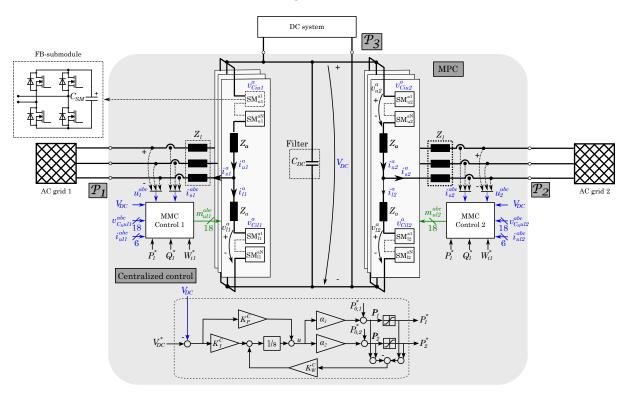

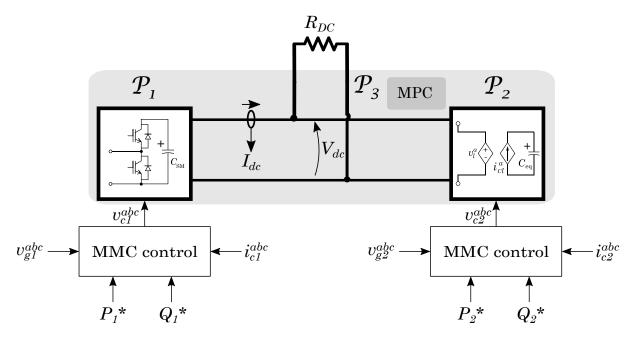

| 23 | Topology and control of the studied topology                                         | 55 |

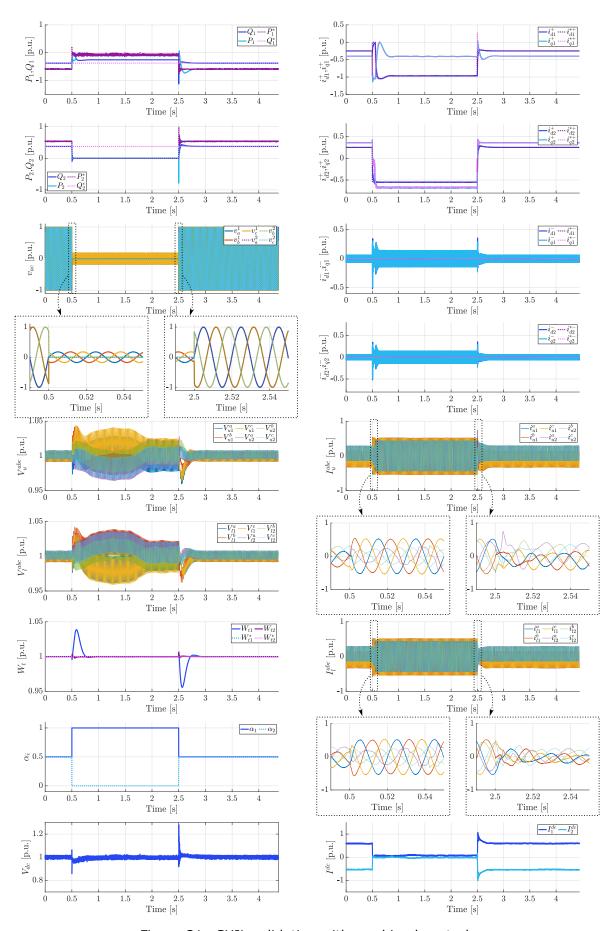

| 24 | Scenarios considered for MPC control validation                                      | 57 |

| 25 | DC voltage and total energy in classical control                                     | 59 |

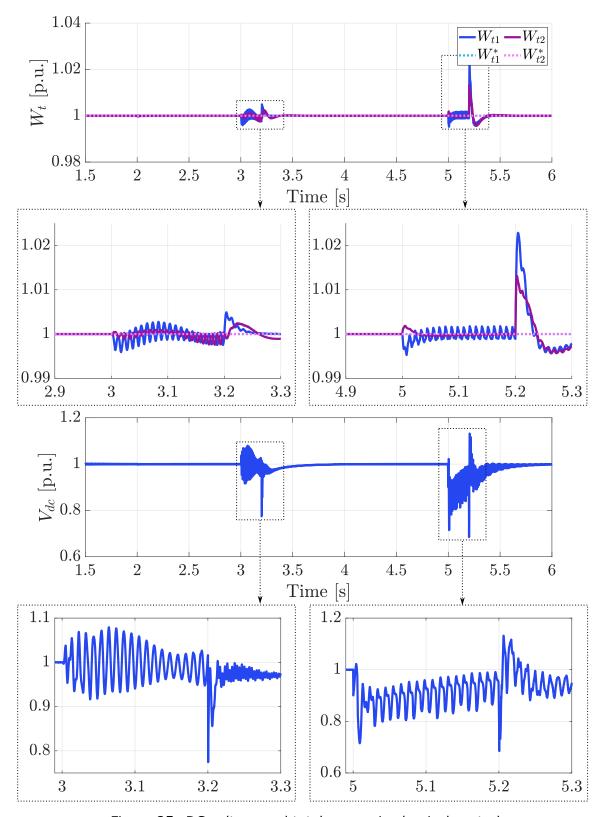

| 26 | DC voltage and total energy results with crossed control                             | 60 |

| 27 | DC voltage and total energy results with crossed control and DC faults               | 61 |

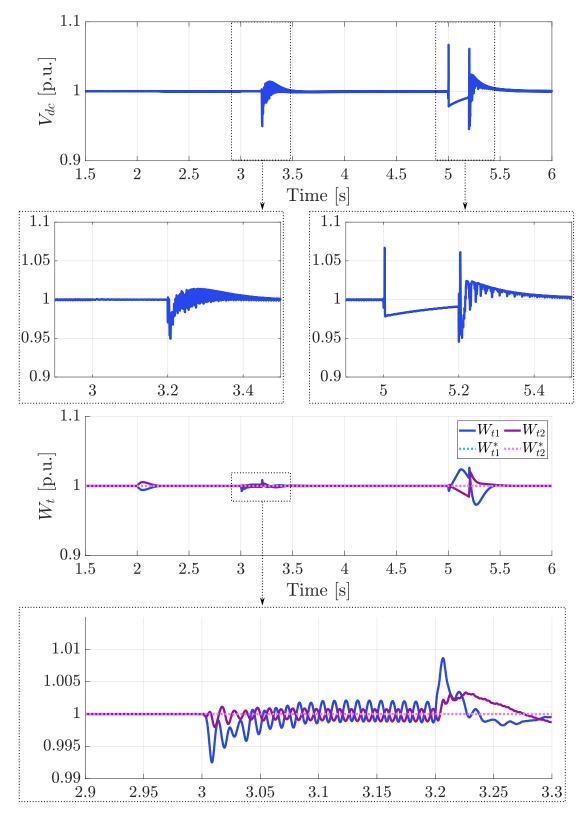

| 28 | DC voltage and total energy with combined control                                    | 63 |

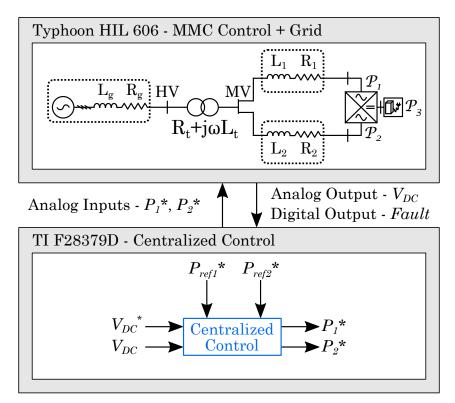

| 29 | Schematic of the CHIL setup                                                          | 64 |

| 30 | Modelling and control inside Typhoon HIL device with CHIL validation                 | 65 |

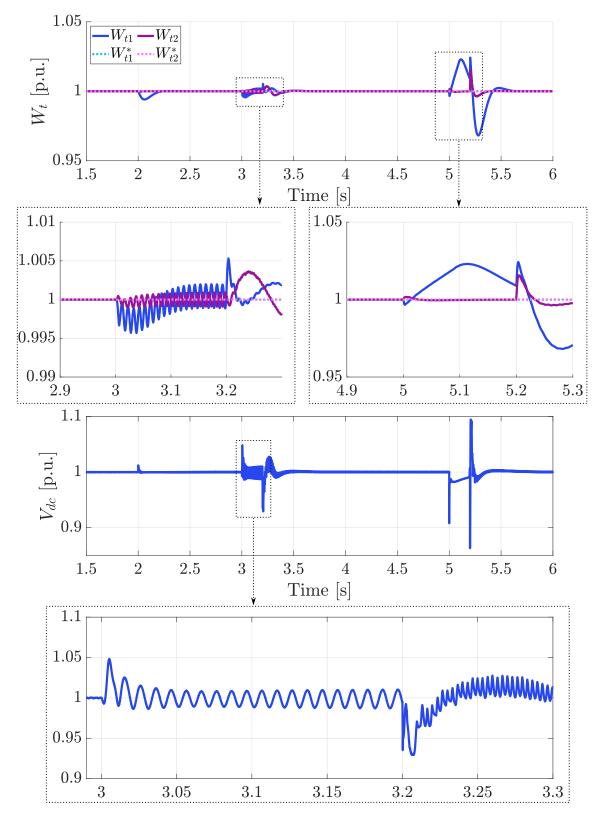

| 31 | CHIL validation with combined control                                                | 66 |

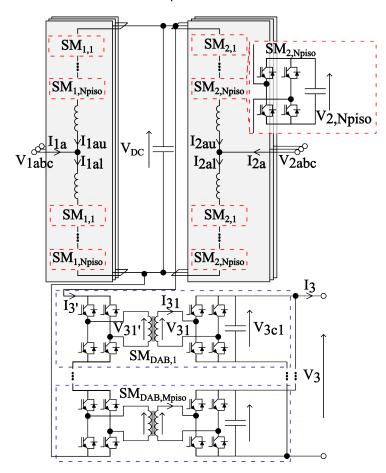

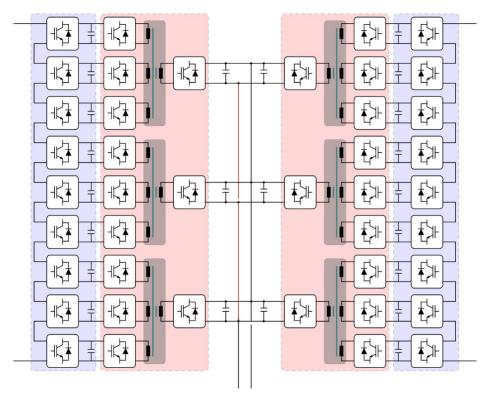

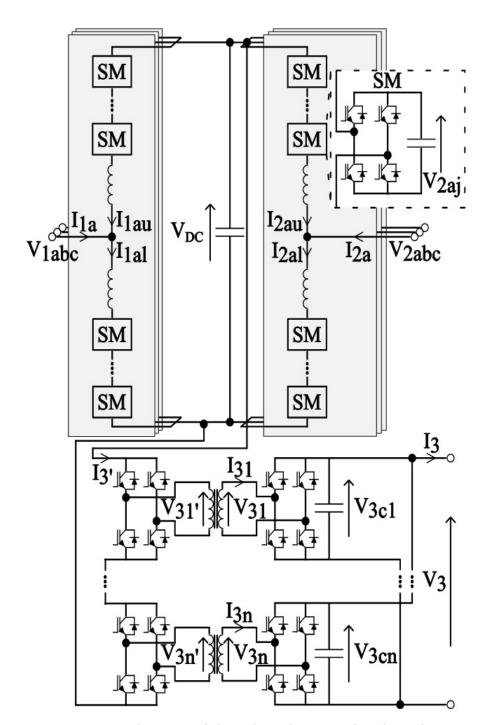

| 32 | Schematic of the selected semi-isolated topology                                     | 69 |

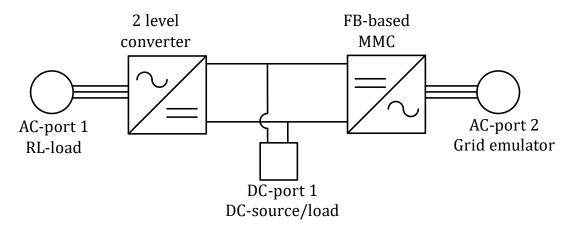

| 33 | Components to make up the lab prototype                                              | 70 |

| 34 | Block diagram of the laboratory setup                                                | 71 |

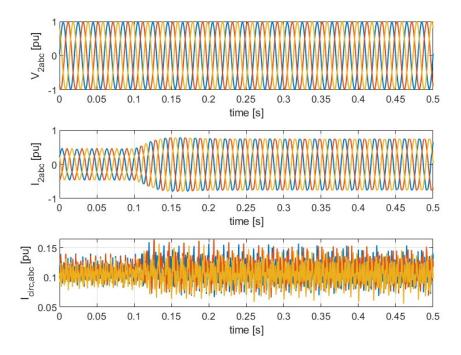

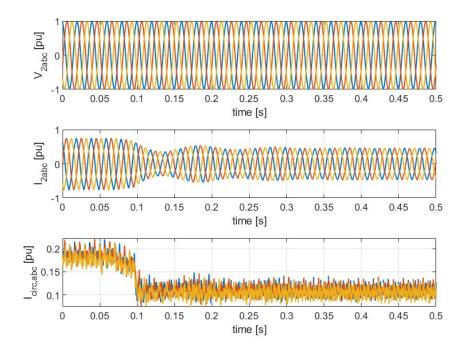

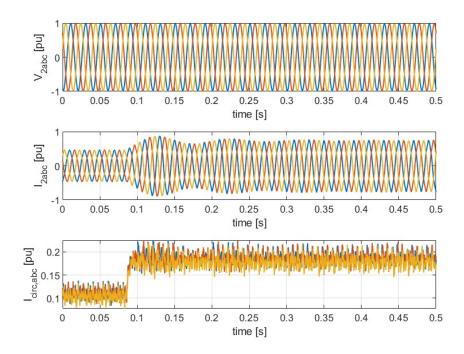

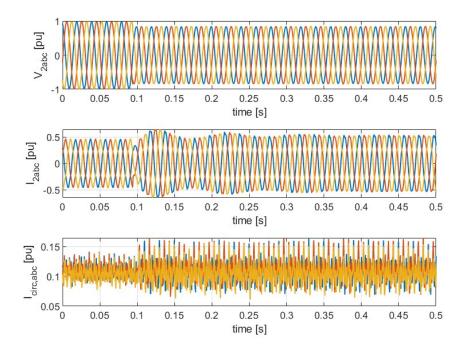

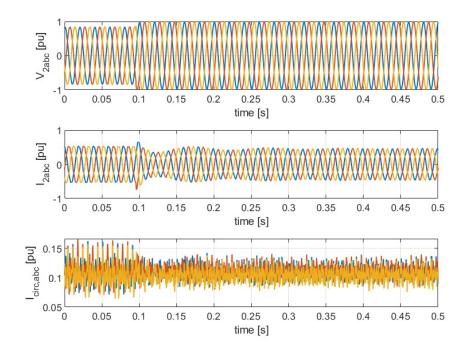

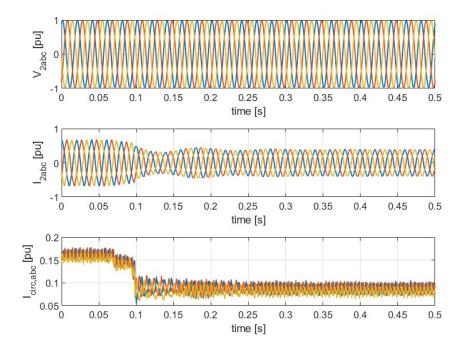

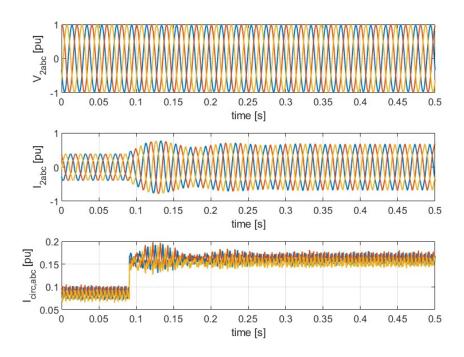

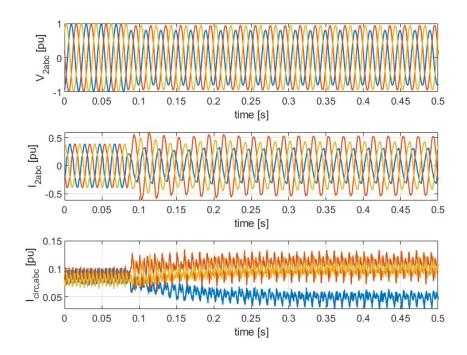

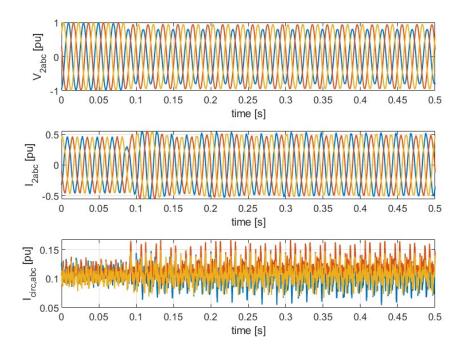

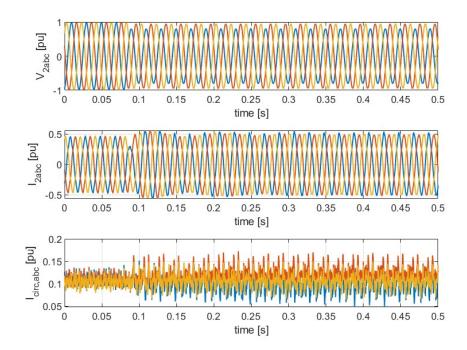

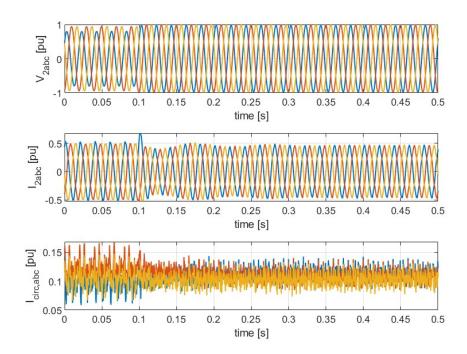

| 35 | Three-phase grid voltages (top), three-phase grid currents (middle) and three-       |    |

|    | phase circulating currents inside MMC phase legs at port 2 (bottom); a reactive-     |    |

|    | power step-up happens at 0.1 s at port 2                                             | 73 |

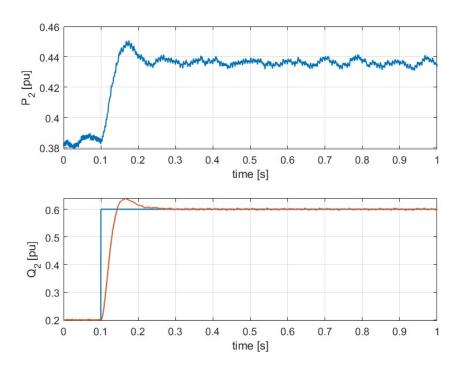

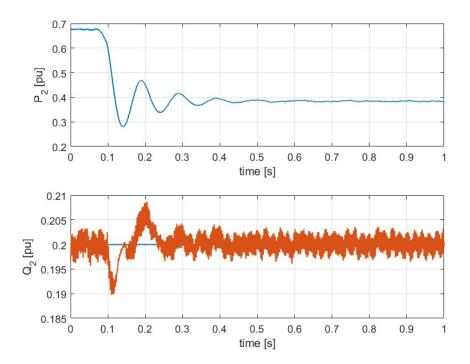

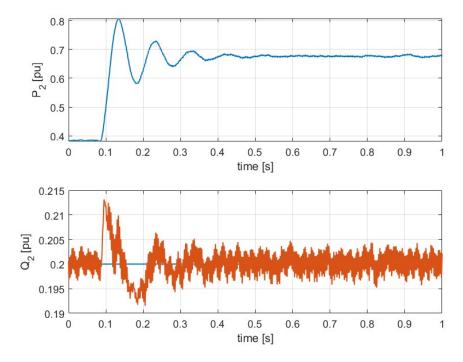

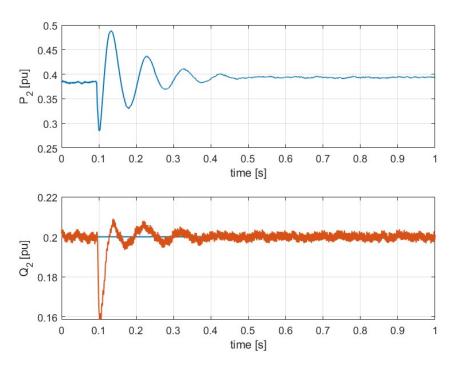

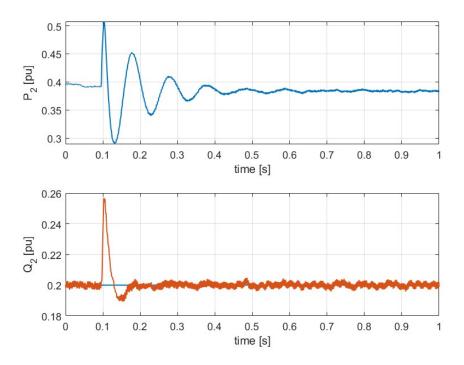

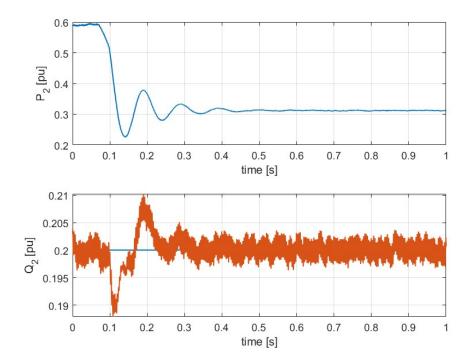

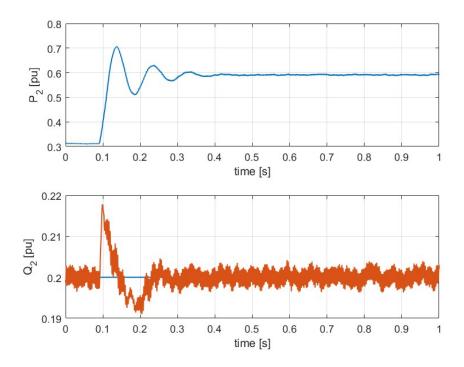

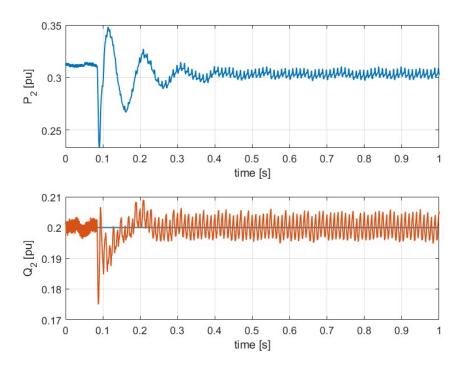

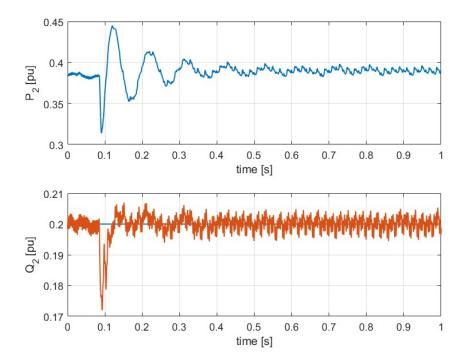

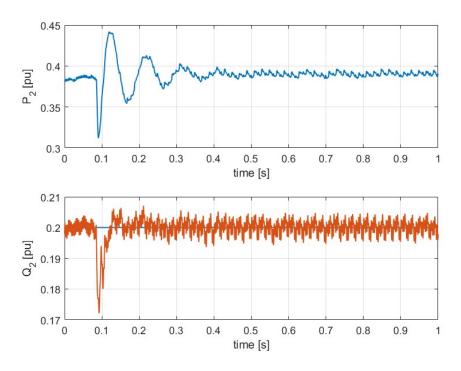

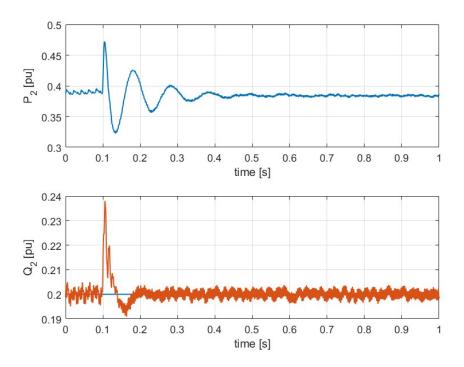

| 36 | Active power from the grid at port 2 (top) and reactive power from the MMC           |    |

|    | at port 2 (bottom); A reactive-power step-up happens at $0.1 \ s$ at port $2$        | 74 |

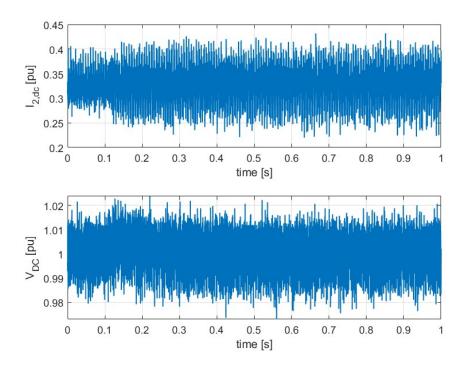

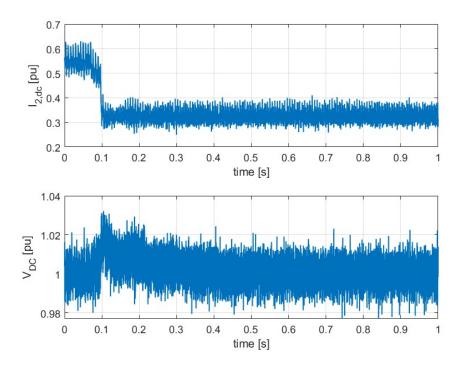

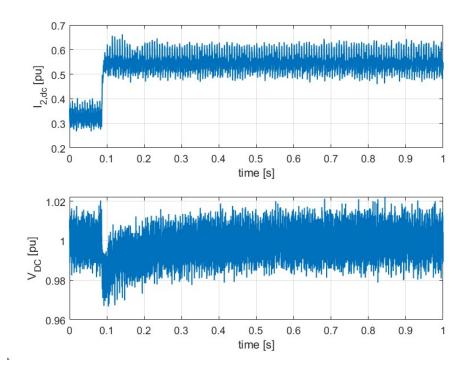

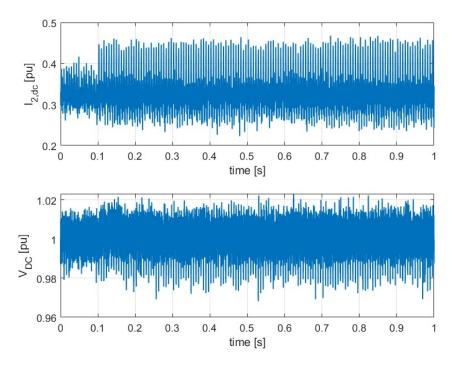

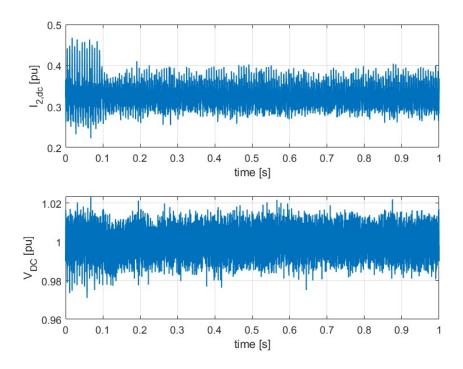

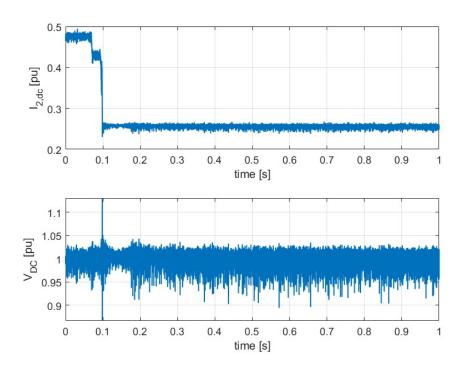

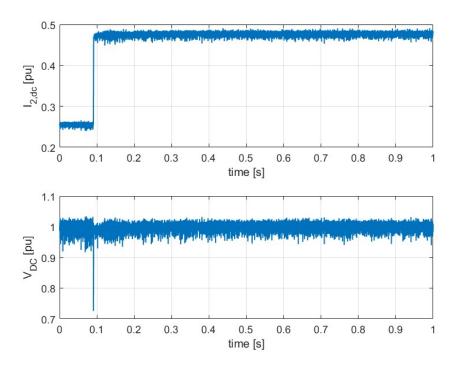

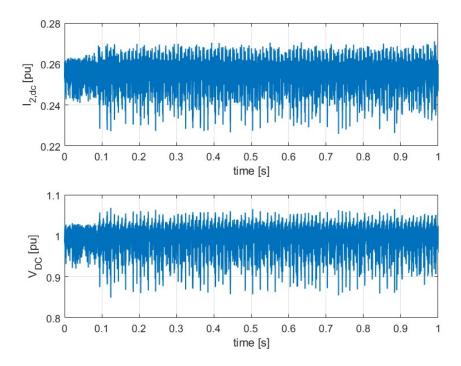

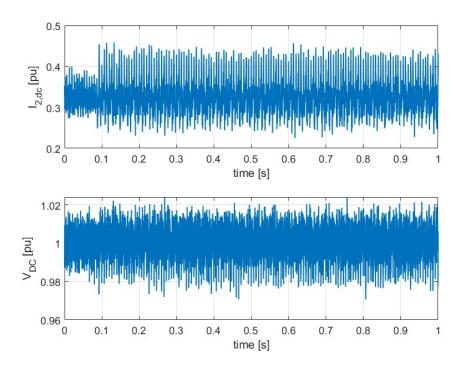

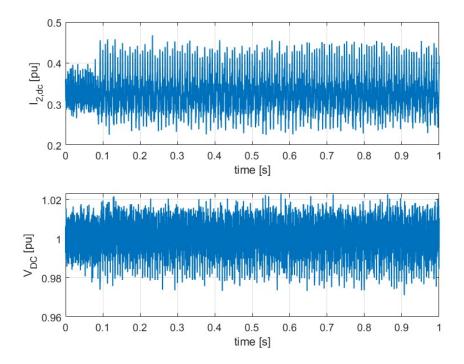

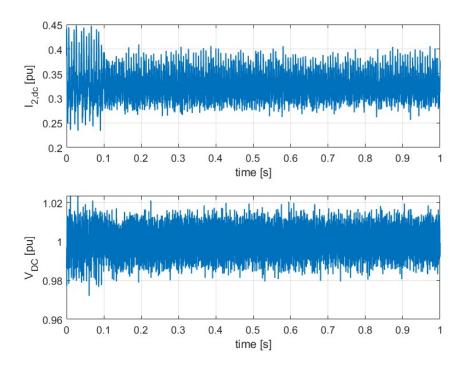

| 37 | DC current from the MMC to the DC-link (top) and the common DC-link voltage          |    |

|    | (bottom) of the MPC; a reactive-power step-up happens at 0.1 s at port 2             | 74 |

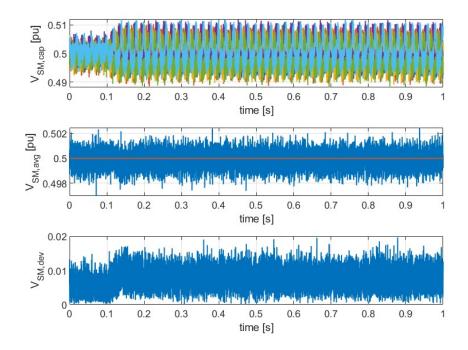

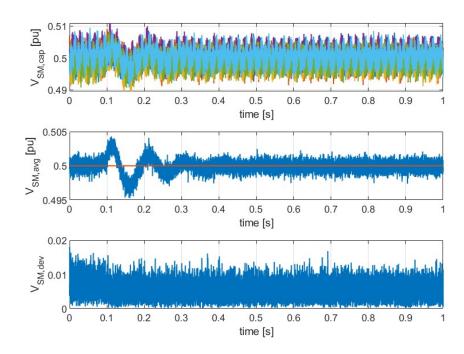

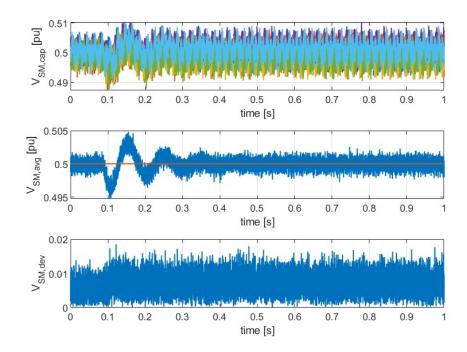

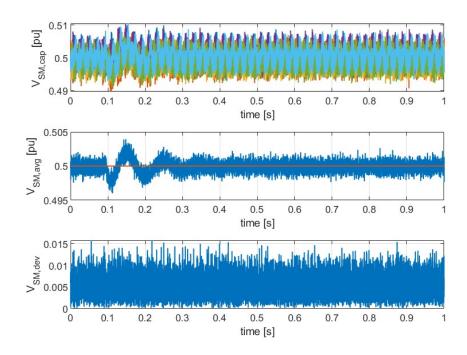

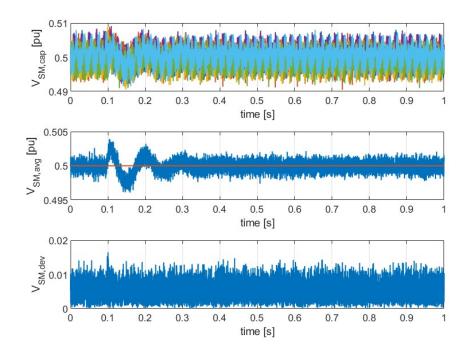

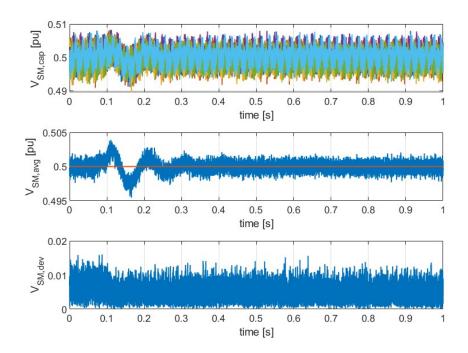

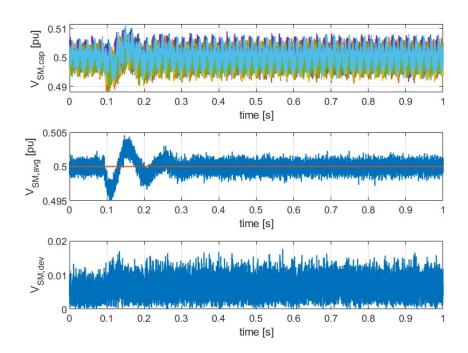

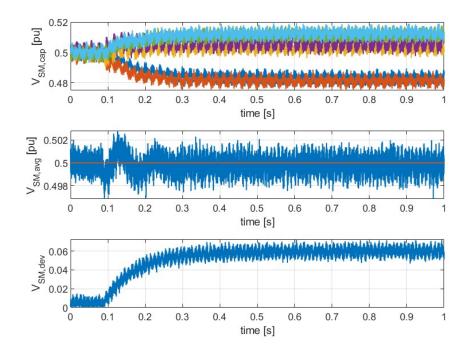

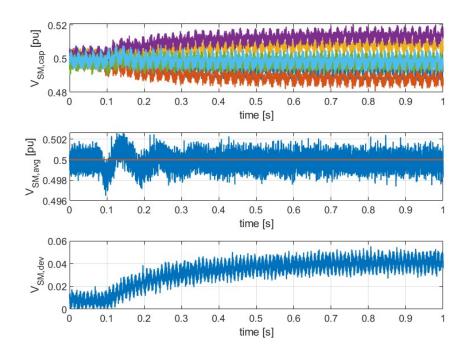

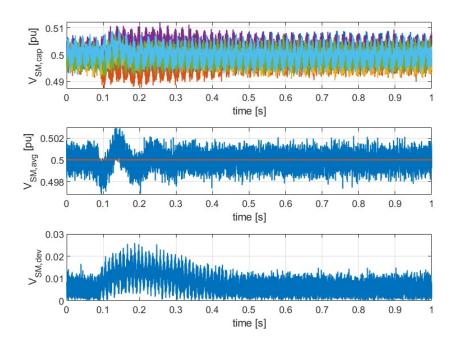

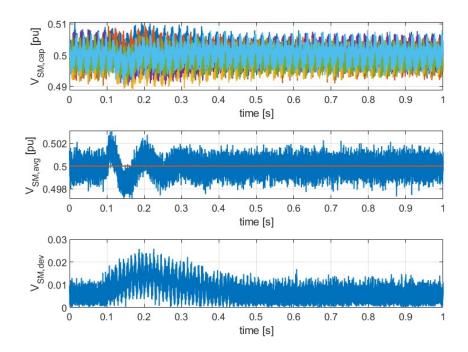

| 38 | Capacitor voltages of one SM per-arm of the MMC at port 2 (top), average SM          |    |

|    | capacitor voltage and its reference (middle) and ratio of maximum deviation          |    |

|    | between the average SM capacitor voltage of each phase-leg of the MMC (bot-          |    |

|    | tom) to the nominal SM capacitor voltage; a reactive-power step-up happens           |    |

|    | at 0.1 s at port 2                                                                   | 75 |

| 39 | Three-phase grid voltages (top), three-phase grid currents (middle) and three-       |    |

|    | phase circulating currents inside MMC phase legs at port 2 (bottom); a load          |    |

|    | step-down happens around 0.1 s at the dc-port                                        | 76 |

| 40 | Active power from the grid at port 2 (top) and reactive power from the MMC           |    |

|    | at port 2 (bottom); a load step-down happens around 0.1 s at the DC-port             | 76 |

| 41 | DC current from the MMC to the DC-link (top) and the common DC-link voltage     |    |

|----|---------------------------------------------------------------------------------|----|

|    | (bottom) of the MPC; a load step-down happens around 0.1 s at the dc-port.      | 77 |

| 42 | Capacitor voltages of one SM per-arm of the MMC at port 2 (top), average SM     |    |

|    | capacitor voltage and its reference (middle) and ratio of maximum deviation     |    |

|    | between the average SM capacitor voltage of each phase-leg of the MMC (bot-     |    |

|    | tom) to the nominal SM capacitor voltage; a load step-down happens around       |    |

|    | 0.1 s at the DC-port                                                            | 77 |

| 43 | Three-phase grid voltages (top), three-phase grid currents (middle) and three-  |    |

|    | phase circulating currents inside MMC phase legs at port 2 (bottom); a load     |    |

|    | step-up happens around 0.1 s at the DC-port                                     | 78 |

| 44 | Active power from the grid at port 2 (top) and reactive power from the MMC      |    |

|    | at port 2 (bottom); a load step-up happens around 0.1 s at the DC-port          | 78 |

| 45 | DC current from the MMC to the DC-link (top) and the common DC-link voltage     |    |

|    | (bottom) of the MPC; a load step-up happens around 0.1 s at the DC-port         | 79 |

| 46 | Capacitor voltages of one SM per-arm of the MMC at port 2 (top), average        |    |

|    | SM capacitor voltage and its reference (middle) and ratio of maximum devia-     |    |

|    | tion between the average SM capacitor voltage of each phase-leg of the MMC      |    |

|    | (bottom) to the nominal SM capacitor voltage; a load step-up happens around     |    |

|    | 0.1 s at the DC-port                                                            | 79 |

| 47 | Three-phase grid voltages (top), three-phase grid currents (middle) and three-  |    |

|    | phase circulating currents inside MMC phase legs at port 2 (bottom); a three-   |    |

|    | phase balanced voltage dip happens around 0.1 s at AC-port 2                    | 80 |

| 48 | Active power from the grid at port 2 (top) and reactive power from the MMC      |    |

|    | at port 2 (bottom); a three-phase balanced voltage dip happens around 0.1 s     |    |

|    | at AC-port 2                                                                    | 81 |

| 49 | DC current from the MMC to the DC-link (top) and the common DC-link voltage     |    |

|    | (bottom) of the MPC; a three-phase balanced voltage dip happens around $0.1\ s$ |    |

|    | at AC-port 2                                                                    | 81 |

| 50 | Capacitor voltages of one SM per-arm of the MMC at port 2 (top), average SM     |    |

|    | capacitor voltage and its reference (middle) and ratio of maximum deviation     |    |

|    | between the average SM capacitor voltage of each phase-leg of the MMC (bot-     |    |

|    | tom) to the nominal SM capacitor voltage; a three-phase balanced voltage dip    |    |

|    | happens around 0.1 s at AC-port 2                                               | 82 |

| 51 | Three-phase grid voltages (top), three-phase grid currents (middle) and three-  |    |

|    | phase circulating currents inside MMC phase legs at port 2 (bottom); a three-   |    |

|    | phase balanced voltage dip is removed around 0.1 s at AC-port 2                 | 82 |

| 52 | Active power from the grid at port 2 (top) and reactive power from the MMC at  |    |

|----|--------------------------------------------------------------------------------|----|

|    | port 2 (bottom); a three-phase balanced voltage dip is removed around 0.1 s    |    |

|    | at AC-port 2                                                                   | 83 |

| 53 | DC current from the MMC to the DC-link (top) and the common DC-link voltage    |    |

|    | (bottom) of the MPC; a three-phase balanced voltage dip is removed around      |    |

|    | 0.1 s at ac-port 2                                                             | 83 |

| 54 | Capacitor voltages of one SM per-arm of the MMC at port 2 (top), average SM    |    |

|    | capacitor voltage and its reference (middle) and ratio of maximum deviation    |    |

|    | between the average SM capacitor voltage of each phase-leg of the MMC (bot-    |    |

|    | tom) to the nominal SM capacitor voltage; a three-phase balanced voltage dip   |    |

|    | is removed around 0.1 s at AC-port 2                                           | 84 |

| 55 | Three-phase grid voltages (top), three-phase grid currents (middle) and three- |    |

|    | phase circulating currents inside MMC phase legs at port 2 (bottom); no AC-    |    |

|    | port 1 and a load step-down happens between 0.05 and 0.1 s at the DC-port.     | 85 |

| 56 | Active power from the grid at port 2 (top) and reactive power from the MMC     |    |

|    | at port 2 (bottom); no AC-port 1 and a load step-down happens between          |    |

|    | 0.05 and 0.1 s at the DC-port                                                  | 85 |

| 57 | DC current from the MMC to the DC-link (top) and the common dc-link voltage    |    |

|    | (bottom) of the MPC; no AC-port 1 and a load step-down happens between         |    |

|    | 0.05 and 0.1 s at the DC-port                                                  | 86 |

| 58 | Capacitor voltages of one SM per-arm of the MMC at port 2 (top), average SM    |    |

|    | capacitor voltage and its reference (middle) and ratio of maximum deviation    |    |

|    | between the average SM capacitor voltage of each phase-leg of the MMC (bot-    |    |

|    | tom) to the nominal SM capacitor voltage; no AC-port 1 and a load step-down    |    |

|    | happens between 0.05 and 0.1 s at the DC-port                                  | 86 |

| 59 | Three-phase grid voltages (top), three-phase grid currents (middle) and three- |    |

|    | phase circulating currents inside MMC phase legs at port 2 (bottom); no AC-    |    |

|    | port 1 and a load step-up happens between 0.05 and 0.1 s at the DC-port        | 87 |

| 60 | Active power from the grid at port 2 (top) and reactive power from the MMC at  |    |

|    | port 2 (bottom); no AC-port 1 and a load step-up happens between 0.05 and      |    |

|    | 0.1 s at the DC-port                                                           | 87 |

| 61 | DC current from the MMC to the DC-link (top) and the common DC-link volt-      |    |

|    | age (bottom) of the MPC; no AC-port 1 and a load step-up happens between       |    |

|    | 0.05 and 0.1 s at the DC-port                                                  | 88 |

| 62 | Capacitor voltages of one SM per-arm of the MMC at port 2 (top), average SM    |    |

|----|--------------------------------------------------------------------------------|----|

|    | capacitor voltage and its reference (middle) and ratio of maximum deviation    |    |

|    | between the average SM capacitor voltage of each phase-leg of the MMC (bot-    |    |

|    | tom) to the nominal SM capacitor voltage; no AC-port 1 and a load step-up      |    |

|    | happens between 0.05 and 0.1 s at the DC-port                                  | 88 |

| 63 | Three-phase grid voltages (top), three-phase grid currents (middle) and three- |    |

|    | phase circulating currents inside MMC phase legs at port 2 (bottom); an unbal- |    |

|    | anced voltage dip happens around 0.1 s at AC-port 2 and a negative-sequence    |    |

|    | AC-side controller is not implemented                                          | 89 |

| 64 | Active power from the grid at port 2 (top) and reactive power from the MMC at  |    |

|    | port 2 (bottom); an unbalanced voltage dip happens around 0.1 s at AC-port     |    |

|    | 2 and a negative-sequence AC-side controller is not implemented                | 90 |

| 65 | DC current from the MMC to the DC-link (top) and the common DC-link voltage    |    |

|    | (bottom) of the MPC; an unbalanced voltage dip happens around 0.1 s at AC-     |    |

|    | port 2 and a negative-sequence AC-side controller is not implemented           | 90 |

| 66 | Capacitor voltages of one SM per-arm of the MMC at port 2 (top), average SM    |    |

|    | capacitor voltage and its reference (middle) and ratio of maximum deviation    |    |

|    | between the average SM capacitor voltage of each phase-leg of the MMC (bot-    |    |

|    | tom) to the nominal SM capacitor voltage; an unbalanced voltage dip happens    |    |

|    | around 0.1 s at AC-port 2 and a negative-sequence AC-side controller is not    |    |

|    | implemented                                                                    | 91 |

| 67 | Three-phase grid voltages (top), three-phase grid currents (middle) and three- |    |

|    | phase circulating currents inside MMC phase legs at port 2 (bottom); an unbal- |    |

|    | anced voltage dip happens around 0.1 s at AC-port 2 and a negative-sequence    |    |

|    | AC-side controller is implemented                                              | 92 |

| 68 | Active power from the grid at port 2 (top) and reactive power from the MMC at  |    |

|    | port 2 (bottom); an unbalanced voltage dip happens around 0.1 s at AC-port     |    |

|    | 2 and a negative-sequence AC-side controller is implemented                    | 92 |

| 69 | DC current from the MMC to the DC-link (top) and the common DC-link voltage    |    |

|    | (bottom) of the MPC; an unbalanced voltage dip happens around 0.1 s at AC-     |    |

|    | port 2 and a negative-sequence AC-side controller is implemented               | 93 |

| 70 | Capacitor voltages of one SM per-arm of the MMC at port 2 (top), average       |    |

|    | SM capacitor voltage and its reference (middle) and ratio of maximum devia-    |    |

|    | tion between the average SM capacitor voltage of each phase-leg of the MMC     |    |

|    | (bottom) to the nominal SM capacitor voltage; an unbalanced voltage dip hap-   |    |

|    | pens around 0.1 s at AC-port 2 and a negative-sequence AC-side controller is   |    |

|    | implemented                                                                    | 93 |

| / I | rnree-phase grid voitages (top), three-phase grid currents (middle) and three- |    |

|-----|--------------------------------------------------------------------------------|----|

|     | phase circulating currents inside MMC phase legs at port 2 (bottom); an unbal- |    |

|     | anced voltage dip happens around 0.1 s at AC-port 2 and a negative-sequence    |    |

|     | and SM-capacitor voltage-unbalance controllers are implemented                 | 94 |

| 72  | Active power from the grid at port 2 (top) and reactive power from the MMC at  |    |

|     | port 2 (bottom); an unbalanced voltage dip happens around 0.1 s at AC-port 2   |    |

|     | and a negative-sequence and SM-capacitor voltage-unbalance controllers are     |    |

|     | implemented                                                                    | 95 |

| 73  | DC current from the MMC to the DC-link (top) and the common DC-link volt-      |    |

|     | age (bottom) of the MPC; an unbalanced voltage dip happens around $0.1\ s$     |    |

|     | at AC-port 2 and a negative-sequence and SM-capacitor voltage-unbalance        |    |

|     | controllers are implemented                                                    | 95 |

| 74  | Capacitor voltages of one SM per-arm of the MMC at port 2 (top), average SM    |    |

|     | capacitor voltage and its reference (middle) and ratio of maximum deviation    |    |

|     | between the average SM capacitor voltage of each phase-leg of the MMC (bot-    |    |

|     | tom) to the nominal SM capacitor voltage; an unbalanced voltage dip happens    |    |

|     | around 0.1 s at AC-port 2 and a negative-sequence and SM-capacitor voltage-    |    |

|     | unbalance controllers are implemented                                          | 96 |

| 75  | Three-phase grid voltages (top), three-phase grid currents (middle) and three- |    |

|     | phase circulating currents inside MMC phase legs at port 2 (bottom); the un-   |    |

|     | balanced voltage dip is removed around 0.1 s at AC-port 2 and a negative-      |    |

|     | sequence and SM-capacitor voltage-unbalance controllers are implemented        | 96 |

| 76  | Active power from the grid at port 2 (top) and reactive power from the MMC     |    |

|     | at port 2 (bottom); the unbalanced voltage dip is removed around $0.1\ s$ at   |    |

|     | AC-port 2 and a negative-sequence and SM-capacitor voltage-unbalance con-      |    |

|     | trollers are implemented                                                       | 97 |

| 77  | DC current from the MMC to the DC-link (top) and the common DC-link voltage    |    |

|     | (bottom) of the MPC; the unbalanced voltage dip is removed around $0.1\ s$     |    |

|     | at AC-port 2 and a negative-sequence and SM-capacitor voltage-unbalance        |    |

|     | controllers are implemented                                                    | 97 |

| 78  | Capacitor voltages of one SM per-arm of the MMC at port 2 (top), average       |    |

|     | SM capacitor voltage and its reference (middle) and ratio of maximum devia-    |    |

|     | tion between the average SM capacitor voltage of each phase-leg of the MMC     |    |

|     | (bottom) to the nominal SM capacitor voltage; the unbalanced voltage dip is    |    |

|     | removed around 0.1 s at AC-port 2 and a negative-sequence and SM-capacitor     |    |

|     | voltage-unbalance controllers are implemented                                  | 98 |

# **List of Tables**

| 1 | Port specification for the two Enhanced Soft Open Point Cases | 19 |

|---|---------------------------------------------------------------|----|

| 2 | Switch requirements for Case 1                                | 34 |

| 3 | Component count tipping points for Case 1                     | 34 |

| 4 | Component count tipping points for Case 2                     | 36 |

| 5 | TAB parameters                                                | 48 |

| 6 | Model validation parameters                                   | 56 |

| 7 | CHIL validation parameters                                    | 65 |

## 1 Executive summary

This report, Deliverable 2.2 of the iPLUG project, overviews the work that has been carried out in WP2 on comparison and experimental validation of medium-voltage multiport power converters (MPCs). For this, various candidate topologies with distinctions in configuration, isolation and converter cells to build the MV topology are compared in order to select the best alternative for MV application. From the comparison, a partly-isolated topology, which combines the good characteristics of the fully non-isolated as well as the fully isolated topologies in terms of performance in normal and fault conditions, flexibility for varying voltage and power levels, and number of components, is selected. Finally, a small-scale and slightly modified laboratory prototype is developed for the selected topology and its performance in both normal and fault conditions is tested to verify the successful operation of the topology.

## 2 Introduction

In line with the EU's commitment to global climate action under the Paris Agreement, modern power systems are increasingly dominated by clean energy sources with net-zero greenhouse gas emissions to achieve the aim of being climate-neutral by 2050. Hence, there is an unquestionable trend to increase the penetration of renewables to unprecedented levels both at transmission and distribution level. In this regard, European Union is targeting a 40% share of renewables by 2030 with the intention to achieve much higher targets by 2050. With this effort in the transition towards more renewable energy production, the use of power converters to interface these sources to the grid is correspondingly increasing. The type and level of these renewable sources is especially high at distribution level and hence the demand for power electronics based solutions to increase the capacity and reliability of the grid is even more important.

At distribution level with significant penetration of renewable sources (such as solar PV and wind power plants), several industrial loads, electrical vehicle charging stations, and energy storage units, power electronics play a vital role in enhancing integration of renewables and energy storage systems, optimal use of the distribution network, and connection of various loads at different voltage levels both with AC and DC. Some of the power-electronic solutions discussed in the literature in the distribution grid for capacity enhancement, improved flexibility, and better controllability include the use of Soft-Open Point (SOP), smart transformers and multiport converters [1–3]. When isolation is required in some of these configurations for medium or high voltage applications and when varying voltage levels are involved, high-frequency based DC-DC converters are important building blocks of the converters. In this regard, dual-active bridge (DAB) based DC-DC converter is the most common configuration. On the other hand, the use of DC-DC converters with multiple active-bridges has the advantage of reliability during faults and reduce the number of modules for medium or high power application [4, 5]. In line with this, WP2 aims to develop suitable multiport converter topologies and their control schemes to enhance MV distribution system's efficiency and utilization. Different multiport converter structures will be investigated and ranked, based on the specific functionalities to be provided to the distribution grid. To achieve this objective, comparison and evaluation of multiport power converters has been performed to select a topology suitable for medium voltage application. Specifically, this report documents tasks 2.3 and 2.4 of WP2 and a summary of the work include:

- 1. Evaluate and rank multiport converter topologies for MV application

- review of various multiport candidate topologies for MV application

- comparison and selection of the best topology based on design flexibility, number

of needed components, fault handling and dynamic performance.

- optimization demonstration of isolation stage with triple-active bridge converter as an example.

- 2. Laboratory validation of selected topology

- Dynamic performance test validation of a non-isolated MV-MPC based on full-bridge(FB) MMC by Typhoon HIL's control- hardware in the loop (CHIL) setup confirming the practical feasibility of the topology.

- Dynamic performance test validation of the selected partly-isolated MV-MPC based on FB-MMC similar to the previous point but with the addition of an isolated DCport and a modified control strategy. Here, the prototype is developed using all hardware as it will be detailed in Chapter 6.

# 3 Identification of a topology for medium-voltage laboratory verification

### 3.1 Application Specifications

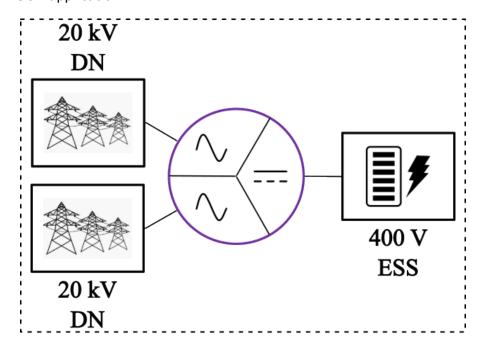

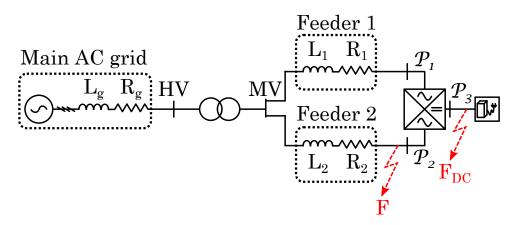

Work Package 2 focuses on the development of multiport power converter solutions for medium voltage applications. Valuable MPC applications are detailed in D1.1. One medium voltage application outlined in D1.1, which will be the focus of this deliverable, is the Enhanced Soft Open Point (ESOP). Figure 1 exhibits an overview of the MPC configuration within an ESOP application.

# **ESOP MPC**

Figure 1: Enhanced soft open point application diagram.

The MV ESOP application involves the interconnection of two MV AC distribution network (DN) feeders with a low voltage (LV) DC energy storage system (ESS). The objective of the MPC ESOP is to interconnect the DN feeders with the DC port to optimize the power flow between the three ports to increase low carbon energy utilization, minimize network costs, and maximize energy availability. Low carbon energy utilization is increased by minimizing steady-state voltage variations of the DN feeders that may constrain distributed energy resources. The supply of customers with cheap local low carbon energy and minimization of network reinforcement can support low network costs. Energy availability can be supported by the collocated ESS, particularly if the MPC is capable of islanded operation. All of this functionality should be achieved with the parallel objective of fault current containment.

Two MV ESOP cases have been specified to represent different voltage gain cases. Case 1 represents a high voltage gain case where there is a large difference in the voltage of the AC DN feeder port with respect to the DC port. Case 2 represents a lower voltage gain scenario. The voltage and power specifications of each port (detailed in Table 1) are derived from a specific DN's characteristics and corresponding ESS sizing, both provided by Spanish DSO Anell. The power level is low due to the derivation from a transformer specification but serves as a conservative low sizing, which highlights the increasing suitability of the MPC topologies as the power level increases.

Table 1: Port specification for the two Enhanced Soft Open Point Cases.

| Port |              | Volt   | age    | Power   | Bidirectional |  |

|------|--------------|--------|--------|---------|---------------|--|

|      |              | Case 1 | Case 2 | rowei   |               |  |

| 1,2  | AC DN Feeder | 20 kV  | 5 kV   | 400 kVA | Yes           |  |

| 3    | DC ESS       | 400 V  | 800 V  | 100 kW  | Yes           |  |

To fulfill the application specifications, the topology will need to:

- Interconnect widely different voltage levels. To achieve this, the AC ports will need to be scalable to integrate the medium voltage level, a large voltage gain will be required to step the MV down to LV, and isolation is expected to be required to contain the potentially high fault current levels.

- Achieve bidirectional and decoupled power capability across all three ports. This will support the optimized transfer of energy across the feeders for steady-state and dynamic objectives.

- Ensure reliability and fault-tolerance that have a low-likelihood of failure and are capable of continuing operation in the case of loss of components, submodules, or ports.

All of this functionality should be achieved with minimal cost, size, and operational complexity and at maximum efficiency.

### 3.2 Exploration of Feasible Conversion Approaches

iPlug Deliverable 1.1 [6] introduced the range of MPC solutions that may be suitable for MV power system applications. The previous work highlighted that conventional two-port non-isolated AC/DC converters were suitable to be scaled to MV levels but that the extension of these configurations to multiport non-integrated solutions would be associated with large numbers of components. Isolated converters were found to offer desirable fault tolerance [7], the limitation of harmonic transfer between medium and low voltages [1], and high voltage gain capability but at the cost of increased port coupling and operational complexity.

They were deemed to require high numbers of components for simple applications but they may be suitable for higher voltage gain applications. Partially-isolated converters were less widely explored for MV levels but may offer a mixture of the benefits of non- and fully-isolated topologies.

The feasibility of a range of topologies for the specific cases detailed in Section 3.1 will be explored in the following subsections. The most suitable topology from the partially-isolated family and the most suitable from the isolated family will be identified from the review, both of which will be carried forward for a detailed analysis in Section 3.3.

Some single-stage converter approaches exist that are capable of interfacing multiple ports in a single conversion device (e.g. direct isolated matrix converters) but they don't offer easy integration of additional ports and experience coupling between ports that could limit the operational capability of the MPC [8]. To ensure the desired decoupling of the MV DN feeders from the LV ESS port, only multi-stage topologies will be considered here-on (which are associated with increased capacitance, sensing, and processing requirements compared to single-stage solutions [9]).

### 3.2.1 Partially-isolated Topologies

The MV AC ports will require a multi-level (ML) conversion configuration to enable the use of cost effective LV rated switches. ML AC/DC converters are often associated with a modular design, flexible operation, and high quality power output [10]. While Cascaded H-bridge (CHB) configurations offer simple and low component multi-level topologies, they cannot support an intermediate DC bus, which is deemed to be necessary to integrate the DC port of the partially-isolated topology. As a result, modular multi-level converter (MMC) configurations will be pursued, which are widely implemented in back-to-back configurations to integrate two AC ports to one another.

MMC submodules (SMs) can be configured as either half- (HfB) or full-bridge (FB). HfBs are composed of only two switches per SM, which enables the modulation of 0 or positive voltages. This results in an intermediate voltage bus that must operated at a fixed voltage, two times larger than the peak AC port voltage. In contrast, FBs are composed of four switches per SM, which enables the modulation of 0, positive, or negative voltages. The ability to modulate negative SM voltages enables the MMC to operate in AC voltage boost mode, where the intermediate DC voltage is lower than the AC port voltage. For fixed AC port voltages, this offers the ability to operate with a lower intermediate voltage and the potential to decrease the number of SMs required in the DC stage. Several papers have explored the optimization of an active front end converter (some also considering a DC/DC stage to integrate one MV AC DN port with a LV DC port) [11–13]. The key conclusions from these studies include:

- HfB MMCs need to be adapted for different AC port voltages using a transformer, whereas, FB MMCs have a flexible modular design that can be adapted for different port specifications [11].

- FB efficiency is degraded for very high modulation indices ( $V_{DC} << V_{AC}$ ) due to large arm currents. A mid-modulation index can offer a balance of efficiency vs low component number [11].

- Hfb SMs have better reliability than FB SMs due to the lower number of components, however, FB MMCs benefit from the robustness to survive SM failure and therefore have a lower mean time between failure compared to HfB MMCs [11].

- FB MMCs are also fault tolerant due to their three voltage level modulation ability, which mitigates the requirements for LV fuse and circuit breakers that would otherwise be necessary [11].

- The SM capacitor requirement increases as the intermediate DC voltage level reduces, which has a large impact on MMC size and weight [12].

- Voltage ripple and harmonics also need to be considered when choosing a modulation index [13].

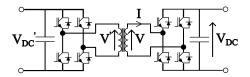

An isolated conversion stage is expected to be required to provide the large voltage gain and fault current protection properties needed to integrate the LV DC port to the MV intermediate DC bus. An example of an isolated DC/DC converter is a dual-active bridge (DAB) converter, which is pictured in Figure 2. A DAB is an isolated, bidirectional, and highly efficient two port DC/DC converter [14] whose power flow can be easily controlled by phase shift.

Figure 2: Dual-active bridge topology.

Although the FB MMCs can operate with a low intermediate DC voltage, the modulation ratio should be limited to avoid the degradation of the converter efficiency and capacitor sizing, meaning that a standard DAB module (using cost-effective LV rated switches) will not be able to link the two DC voltages [15]. Instead, series-connection of the DAB modules can be considered.

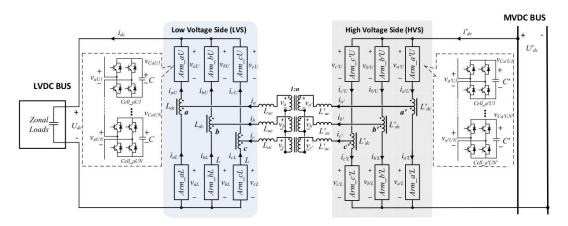

The isolated Modular Multilevel DC Converter (iM2DC) (pictured in Figure 3) offers series connection of half-bridge or full-bridge submodules to convert a medium voltage DC voltage to a high-frequency (HF) AC voltage. The AC voltage is then fed to a transformer winding

whose secondary side is interfaced by a similar (but not necessarily identical) HF AC to DC voltage conversion stage [16].

Using FB SMs, the iM2DC is also capable of modulating three voltage levels, which supports the rapid dissipation of cable inductor energy and the independence of AC and DC voltages [16]. However, this topology incorporates a large number of components (including six sets of series SMs and three two-winding transformers) and requires a degree of symmetry around the isolation stage which does not match the medium voltage-low current to low voltage-medium current characteristics of the MPC.

Figure 3: Isolated modular multilevel DC converter topology. Figure from [7].

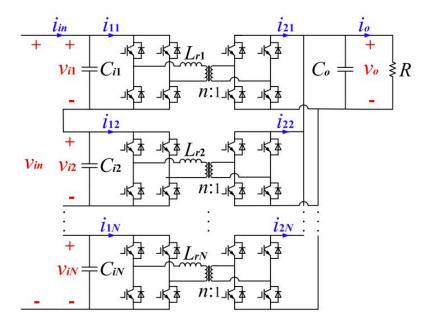

Alternatively, an Input-series Output-parallel (ISOP) multi-DAB configuration [7] could be used, which better matches the MPC ESOP's voltage and current characteristics. An example of an ISOP configuration is pictured in Figure 4. The ISOP connects DAB modules in series on the higher voltage side, utilizes the fundamental properties and control of the DAB module to transfer power from one side to another, and connects the lower voltage side in parallel. The ISOP configuration allows the use of identical LV-rated HF switches on both sides of the converter (assuming that the low voltage fits within the rating of the switch). ISOP has been shown to exhibit soft switch on (with an inductor on the primary side), which can offer lower switching losses, higher switching and transformer frequencies, and therefore the lower sizing of passive components [17]. The higher switching frequency also mitigates harmonic current and voltage components, allowing the smaller sizing of DAB module capacitors.

A MV AC to LV DC application using MMC plus ISOP configuration was found to achieve a reduced number of switches and HF transformers compared to a Solid-state Transformer in [18]. The number of components for this application was found to reduce further by using a FB MMC with low intermediate DC bus in [11].

Both of the two feasible DC/DC conversion approaches for the intermediate bus to LV port offer good scalability to integrate large and variable voltage levels (depending on the

Figure 4: Input-series Output-parallel converter topology. Figure from [19]

specific application). However, they differ in terms of the following key features. The iM2DC:

- Is expected to require a large number of components and have less suitable voltage and current characteristics for the given DC/DC conversion.

- A higher device rating is required to enable devices to support the sum of AC and DC components, which degrades the efficiency, constrains switching and transformer frequencies, and increases the requirement for passive component sizing [17].

- Negative voltage modulation allows the decoupling of DC and AC sides. Although a MV fault will isolate the LV port, a LV fault will simply be observed as a load change allowing the MV port to maintain normal operation [7].

#### While the ISOP:

- Is capable of relatively simple decoupled operation of DAB modules, which fit the voltage and current characteristics of the given DC/DC conversion well.

- Requires fault identification to switch to fault mode (which drives the shutdown of the entire two-port ISOP converter) in the case of both LV and MV faults [7].

- The series connection of DAB modules on the medium voltage side may degrade converter robustness to switch failure.

Although the ISOP converter exhibits worse two port fault characteristics, fault behavior hasn't been explored for MPC configurations, where it may be possible to shutdown

the ISOP converter but maintain back-to-back operation of the two MMCs (and therefore achieve similar fault characteristics as the iM2DC). Considering this feature, the simplicity of operation, and the suitability of the configuration for the MV DC to LV DC application, the ISOP will be selected as the DC/DC stage of the partially isolated converter. Figure 5 exhibits the configuration of this winning topology from the partially-isolated family, which will be carried forward for a detailed comparison with the winner from the isolated family.

Figure 5: Partially-isolated topology winner: Back-to-back full-bridge modular multilevel converter with input-series output-parallel dual-active bridge topology.

### 3.2.2 Isolated Topologies

To achieve isolation of all ports from one another, triple- (TAB) or multi-active bridge (MAB) modules will be required to interface the three ESOP ports together. A TAB (pictured in Figure 6) uses the same operating principles as a DAB; a DC input voltage is converted to a HF AC voltage using an active bridge module. Three active bridge modules are interconnected using three independent windings around a single transformer core. A MAB extends the configuration by adding additional active bridge and winding pairs to integrate every additional port.

Figure 6: Triple/multi-active bridge module. Figure from [14]

TABs and MABs possess similar characteristics to DABs: isolation by the HF transformer, voltage gain via turns ratio, bidirectional power flow via phase shift control, and zero voltage switching ability. However, the topologies experience more complicated magnetic coupling and circulating current issues that worsen with increasing numbers of ports [20]. Control solutions exist to mitigate these issues but can depend on internal models that have varying degrees of accuracy and complexity.

Extending the iM2DC configuration to accommodate three DC ports (each port using three HF AC phases that would each be converted using an allocated MMC leg) would require a large number of components (at least 50 % more compared to a DAB configuration) and complex operation just to establish DC voltages. Additional stages would be required to convert the DC voltages to the MV AC ports. Such a configuration will not be considered further.

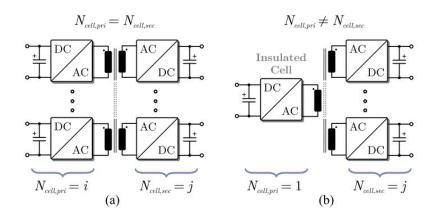

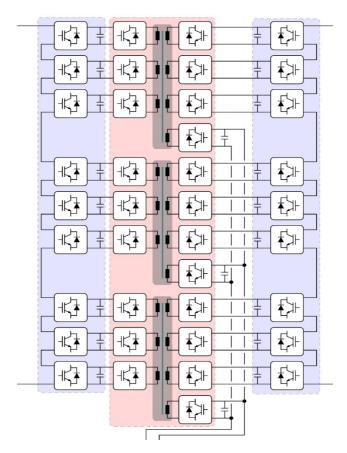

Alternatively, multiple TAB or MAB modules can be configured to integrate multiple ports with varying voltage and current characteristics. Two configurations of a multi-MAB configuration derived from [21] are pictured in Figures 7 and 8. Both configurations use a CHB ML AC/DC conversion approach due to the independence from a single intermediate DC bus and instead the direct connection of active bridges to the AC/DC SM's voltages. The CHB offers half the number of cells compared to a FB MMC, simple operation, and smaller SM capacitance [22, 23].

Figure 7 uses a seven port MAB module to interface a group of three CHB SMs from one AC port to an identical group of three CHB SMs from the other AC port. An additional winding and active bridge pair is allocated in the MAB module to feed the DC port. Additional modules are then connected to interface the additional groups of CHB SMs that make up the MV AC port (as well as contributing to the DC port). The MAB configuration is flexible to be fit to the voltage and current characteristics of the application, where more CHB SM-linked AB pairs can be grouped with a single DC port-linked AB as the ratio of AC port power

to DC port power increases. Figure 8 introduces an additional intermediate DC bus that interfaces asymmetrical CHB SM-linked MAB modules and feeds the DC port (either directly or through its own DC/DC converter). Both configurations can maintain power transfer in the case of CHB SM or active bridge failures (but at the cost of SM capacitor imbalance).

Figure 7: Multi multi-active bridge topology with intermediate AC stage. Topology derived from [21]

The topology in Figure 7 is selected as the winner of the isolated family due to the lower number of components compared to that in Figure 8 while maintaining similar reliable operational characteristics.

## 3.3 Comparison of Winning Topologies

The previous sections have refined reviewed topologies to identify the most feasible partially-isolated and isolated solutions to fulfill the ESOP MPC application. In this section, a detailed comparison of the topologies pictured in Figure 5 and Figure 9 is presented for the purposes of selecting a final topology for laboratory verification. The detailed comparison in the following subsections includes an analysis of component numbers for the two ESOP cases and a qualitative discussion and scoring of the critical operational characteristics.

Figure 8: Multi multi-active bridge topology with intermediate DC stage. Topology derived from [21]

### 3.3.1 Number of Components

The number of components of each topology is compared as a function of different variable parameters as a proxy for the size and cost. The topologies are examined for both ESOP cases: Case 1 requires the larger voltage gain from 20 kV AC to 400 V DC, while Case 2 requires a lower voltage gain from 5 kV AC to 800 V DC.

The voltage blocking ability of low frequency FB switches is assumed to be 3.3 kV and the voltage blocking ability of high frequency active bridge switches is assumed to be 1.2 kV. Both switch types are limited to operate with a utilization factor of 0.65. These specifications represent an optimal setting utilized for a two port MV AC to LV DC MMC plus ISOP configuration in [11]. Table 2 details the exact voltage and current requirements of the topology components considering these voltage blocking abilities and the sizing of the topologies for Case 1.

**Derivation of the Partially-isolated Topology's Components** Not considering the DC voltage level, the number of MMC FB SMs required to interface to one phase of the MV AC voltage is defined by  $N_{P.Iso,AC}$

$$N_{P.Iso,AC} = 2 * ceil(\frac{\hat{V}_{AC}}{V_{SM,FB}})$$

(1)

Figure 9: Isolated topology winner: Cascaded H-bridge with multi-active bridge.

$\hat{V}_{AC}$  is the peak line-line AC voltage and  $V_{SM,FB}$  is the voltage blocking capability (considering switch utilization) of the FB switches. To generate a given intermediate DC voltage  $V_{MVDC}$  an additional set of  $N_{P.Iso,DC}$  SMs is required per phase of the MMC

$$N_{P.Iso,DC} = ceil(\frac{V_{MVDC}}{V_{SM,FB}})$$

(2)

The lower the modulated intermediate DC voltage the lower the number of MMC SMs required. A non-zero intermediate DC voltage is required to offer the connection point for the ISOP DC/DC converter.

Considering the two sets of identical three phase MMCs for the ESOP application (where  $\hat{V}_{AC1} = \hat{V}_{AC2}$ ),  $6N_{P.Iso} = 6(N_{P.Iso,AC} + N_{P.Iso,DC})$  FB SMs will be required for the partially isolated topology. Each FB SM  $SM_{FB}$  will include four two quadrant LF switches  $S_{FB}$  and one SM capacitor  $C_{FB}$ . Each MMC leg will require one filter inductor  $L_f$  (aggregated representation of upper and lower inductance). One intermediate DC capacitance  $C_{MVDC}$  is required to interface the back-to-back MMCs to the ISOP stage.

The number of components required for the back-to-back MMC stage of the partially-

isolated topology can be defined as  $N\underline{o}C_{MMC}$

$$N_{\underline{o}}C_{MMC} = 6[N_{P.Iso} * SM_{FB} + L_f] + C_{MVDC} = 6[N_{P.Iso} * (4S_{FB} + C_{FB}) + L_f] + C_{MVDC}$$

(3)

The FB switches  $S_{FB}$  must withstand  $V_{SM,FB}$ . If there is no DC power transfer each leg (and therefore series-connected FB SM) experiences half the AC phase current  $0.5\hat{I}_{AC}$ . The legs must also share the current  $I_{DC,ph}$  associated with the power transfer from the AC side to DC side, which will be at most a third of the rated power of the AC port  $P_{AC}$

$$I_{DC,ph} = \frac{P_{AC}}{3V_{MVDC}} = \frac{\hat{V}_{AC}\hat{I}_{AC}}{2V_{MVDC}} \tag{4}$$

The total current through each FB switch is  $\hat{I}_{FB}$

$$\hat{I}_{FB} = 0.5\hat{I}_{AC} + I_{DC,ph} \tag{5}$$

$M_{P.Iso}$  DAB modules are required to interface the intermediate DC bus to the LV DC port. Each DAB module is assumed to have a fixed voltage blocking ability  $V_{SM,AB}$ .  $M_{P.Iso}$  is a function of the intermediate DC voltage with respect to the active bridge's voltage blocking ability

$$M_{P.Iso} = ceil(\frac{V_{MVDC}}{V_{SM,AB}})$$

(6)

Each DAB module includes two active bridge SMs  $SM_{AB}=2(4S_{AB}+T.W.)$ , which is composed of active bridge switches  $S_{AB}$  and transformer windings T.W., one transformer core T.C., and one LV output capacitor  $C_{LVDC}$ .

The number of components that the ISOP DC/DC conversion stage requires is defined as  $N \underline{o} C_{ISOP}$

$$N_{\underline{o}}C_{ISOP} = M_{P.Iso}[2 * SM_{AB} + T.C. + C_{LVDC}] = M_{P.Iso}[2(4S_{AB} + T.W.) + T.C. + C_{LVDC}]$$

(7)

Assuming a 1:1 turns ratio on the primary and secondary sides of the DAB transformers, the current flowing through the active bridge switches  $I_{LVDC,AB}$  depends on their share of the power flowing between the intermediate DC bus and the LV DC port  $P_{LVDC}$

$$I_{LVDC,AB} = \frac{P_{LVDC}}{M_{PLso} * V_{LVDC}} = \frac{I_{LVDC}}{M_{PLso}}$$

(8)

The lower the modulated intermediate DC voltage (via negative SM insertion by the FB MMC) the lower the number of SMs required in both the MMC and ISOP stage. However, for a given power transfer, a lower intermediate DC voltage will drive an increase in DC current  $I_{DC,ph}$  and therefore associated losses. The power rating of the ESOP MPC based on the Anell specifications has a very low power rating that won't be significantly affected

by large modulation ratios, but consideration needs to be made when scaling up to larger power levels.

Another downside of large FB MMC modulation ratios is the increased number of negative SM voltages that are inserted. As the overmodulation increases:

- Circulating energy increases [18]

- The lower number of series components and injection of negative voltages can require higher switching frequencies and associated losses [10]

Overall the benefit of FB MMC overmodulation to lower the intermediate DC voltage needs to be optimized to balance all of these features. [11] finds that the benefit of a lower DC voltage for lower component numbers increases with larger switch voltage blocking capabilities. An optimal efficiency configuration was identified with MMC FB switches rated at  $V_{SM,FB}=3.3\ kV$  (switching at  $f_{Sw}=0.1:1\ kHz$ ) and ISOP active bridge switches rated at  $V_{SM,AB}=1.2\ kV$  (switching at  $f_{Sw}=15\ kHz$ ). The sizing study in this deliverable uses the same switch ratings.

**Derivation of the Isolated Topology's Components** The isolated topology uses two identical three phase CHBs to integrate the two MV AC ports. For a given FB switch voltage blocking capability, the CHB requires half the number of series SMs  $N_{Iso}$  to integrate an AC voltage. However, the CHB's SMs are directly connected with the active bridge SMs of the MAB modules, whose switches have to be operated at higher frequency and will therefore be rated to a lower voltage blocking ability. Accordingly, the number of series CHB SMs must be defined as a function of this active bridge voltage blocking ability

$$N_{Iso} = \frac{\hat{V}_{AC}}{V_{SM,AB}} \tag{9}$$

Each CHB SM is assumed to be identical to the partially-isolated FB SMs, however, would be able to utilize lower voltage rated FB switches.

Each CHB leg uses a filter inductor, which is also assumed to be equal to the aggregated filter inductor for each leg of the MMC.

Considering the equal rating of both AC ports, the number of components required for the two three phase CHBs is defined as  $N_{\underline{o}}C_{CHB}$

$$N_{\underline{o}}C_{CHB} = 6[N_{Iso} * SM_{FB} + L_f] = 6[N_{Iso}(4S_{FB} + C_{FB}) + L_f]$$

(10)

The CHB FB switches experience the full AC phase current but similar to the MMC switches can switch at LF

$$\hat{I}_{FB} = \hat{I}_{AC} \tag{11}$$

Three sets of  $M_{Iso}$  MAB modules are required to interface the two sets of three phases of  $N_{Iso}$  CHB SMs to one another and the LVDC port.  $M_{Iso}$  is defined to ensure that the number of CHB SM pairs (connecting the two AC ports) are grouped with one LV DC assigned active bridge around a transformer core proportionally to the power rating of the AC and DC ports

$$M_{Iso} = ceil(\frac{N_{Iso}}{P_{AC}/P_{LVDC}})$$

(12)

The number of MAB modules may also be varied away from the proportional power ratio for techno-economic reasons. For example,  $M_{Iso}$  could be increased to mitigate operational complexities associated with a large number of active bridges around a single transformer core or could be reduced to reduce the number of expensive transformer core components.

Each active bridge SM is assumed to be identical to those in the ISOP converter, including four active bridge switches and one transformer winding. The LV DC active bridges also require an output capacitor  $C_{LVDC}$ .

The number of components required for the multi-MAB isolated DC/DC stage is defined as  $N \underline{o} C_{MMAB}$

$$N_{\underline{o}}C_{MMAB} = 3[2N_{Iso} * (4S_{AB} + T.W.) + M_{Iso}(T.C. + 4S_{LVDC} + T.W. + C_{LVDC})]$$

(13)

The active bridge switches interconnecting the AC ports must withstand a share of the AC power transfer

$$I_{AB} = \frac{P_{AC}}{3N_{Iso}V_{SM,FB}} = \frac{\hat{V}_{AC}\hat{I}_{AC}}{2\hat{V}_{AC}} = 0.5\hat{I}_{AC}$$

(14)

The LV active bridge switches depend on the given active bridge's share of the LV DC power transfer and the LV DC voltage, which is assumed to be equal to the active bridge's voltage blocking rating

$$I_{LVDC,AB} = \frac{P_{LVDC}}{M_{Iso}V_{LVDC}} = \frac{I_{LVDC}}{M_{Iso}}$$

$$\tag{15}$$

All of the active bridge switches must switch at high frequency.

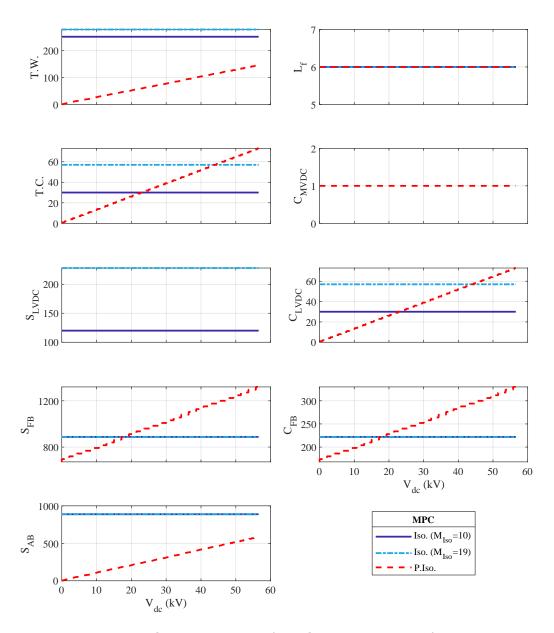

**Results: Case 1** Figure 10 exhibits the results of the component count for the ESOP Case 1. The number of components are pictured as a function of the intermediate DC voltage level. Only the partially-isolated topology's number of components varies with the modulated intermediate DC voltage. As the DC voltage increases the number of MMC SMs increases (from a baseline of  $N_{P.Iso} = N_{P.Iso,AC} = 42$  for  $V_{DC} = 0$ ) as does the number of ISOP DAB modules.

The isolated topology does not have an intermediate DC bus, hence the lack of impact on its number of components. Two configurations of the isolated topology are pictured. Both configurations require the same number of CHB SMs to interface the fixed AC voltage

Figure 10: Comparison of component numbers for Case 1:  $2x\ 20\ kV\ AC\ DN$  ports and  $1x\ 400\ V\ DC\ ESS\ port.$

$(N_{Iso}=37)$ , which is higher than the number of MMC SMs per arm for  $V_{MVDC}=0$  due to the constraint of the CHB SMs to the lower high frequency active bridge switch rating. One configuration has 10 MAB modules  $(M_{Iso}=10)$ , which is calculated to allocate the same ratio of CHB SM-linked active bridge pairs to LV DC port-linked active bridges as the AC to DC port power rating (using eq 12). This configuration of MAB modules groups four CHB SM-linked active bridge pairs (eight active bridges) with a single LV DC port-linked active bridge, resulting in nine active bridges around a single transformer core. A second configuration reduces the operational complexity associated with the high number of active bridges per MAB module by increasing the number of modules to  $M_{Iso}=19$  and therefore

reducing the number of active bridges per transformer core to five.

Both configurations of the isolated topology use a much larger number of transformer windings T.W. and active bridge switches  $S_{AB}$  than any of the partially-isolated configurations. The partially-isolated topology uses identical active bridge switches on both primary and secondary sides of the ISOP DAB modules, hence the many more LV DC switches  $S_{LVDC}$  required for the isolated topology. The more operationally complex  $M_{Iso}=10$  isolated configuration has a lower number of transformer windings, transformer cores T.C., LV DC switches, and LV DC capacitors  $C_{LVDC}$  than the less operationally complex  $M_{Iso}=19$  configuration.

The partially isolated topology may require an intermediate MV DC capacitor  $C_{MVDC}$  and also requires more FB switches  $S_{FB}$  and capacitors  $C_{FB}$  when operating with a high intermediate DC voltage. Two tipping points are shown in Table 3 where the partially-isolated topology moves below the  $M_{Iso}=10$  isolated topology in terms of component number: the first when the partially-isolated topology operates with an intermediate voltage of  $V_{MVDC}=22.62\ kV$  and the second when  $V_{MVDC}=17.16\ kV$ .

At the lower tipping point the partially-isolated topology possesses a lower number of all components than the  $M_{Iso}=10$  topology. At the higher tipping point the partially isolated topology possesses a lower number of all components other than FB switches and capacitors. The partially-isolated topology's number of FB components is the most sensitive component-type to the intermediate DC voltage (despite their higher blocking ratio compared to the active bridge components) due to the two sets of three phase MMC legs that accelerate the increase.

Although it would be desirable to minimize the number of all components, the higher tipping point DC voltage level is deemed to be an acceptable operating characteristic due to the partially-isolated topology's low number of expensive transformer cores, lower number of LV DC capacitors, and significantly lower number of transformer windings, LV DC switches, and active bridge switches. The higher intermediate DC voltage will also achieve improved efficiency compared to a lower operating condition. The intermediate DC voltage  $V_{MVDC}=22.62\ kV$  requires a modulation ratio of m=2.5, which fits within explored modulation ratios for similar two port applications (e.g. m=1.88:3.76 in [18] and m=0.8:5 in [11]) and is therefore assumed to be feasible for the ESOP application. Additional work should explore the optimal modulation ratio to identify its impact on arm energy ripple (with impacts on SM capacitor sizing requirements) and circulating currents (with impacts on converter efficiency) as well as the number of components.

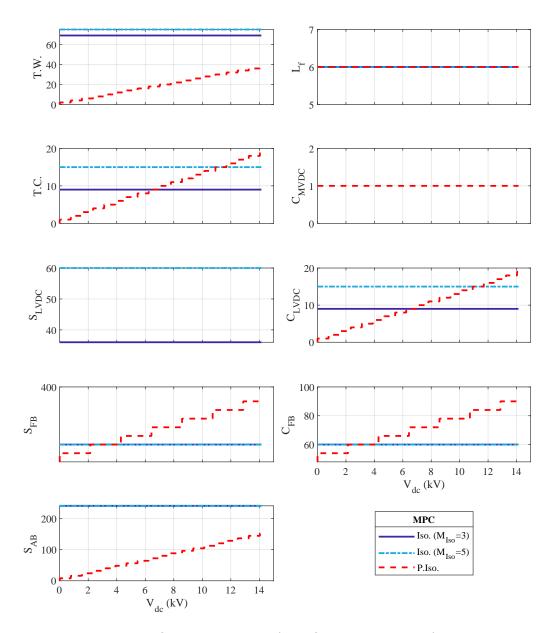

**Results: Case 2** Figure 11 exhibits the results of the component comparison for ESOP Case 2, which includes lower AC port voltages  $V_{AC}=5\ kV$  and a higher LV DC port voltage

Table 2: Switch requirements for Case 1.

|            |        | Switch Requirement    |                |          |               |                   |       |               |               |

|------------|--------|-----------------------|----------------|----------|---------------|-------------------|-------|---------------|---------------|

| Component  | Case   | Partially-isolated    |                |          |               | Isolated          |       |               |               |

|            |        | $V\left( V ight)$     | I(A)           | $f_{Sw}$ | Device        | $V\left( V ight)$ | I(A)  | $f_{Sw}$      | Device        |

| $S_{FB}$   | 1<br>2 | 2145                  | 15.94<br>14.06 | LF       | IGBT          | 780               | 16.33 | LF            | IGBT          |

| $S_{AB}$   | 1<br>2 | 780                   | 5.83<br>4.42   | HF       | SiC<br>MOSFET | 780               | 8.17  | HF            | SiC<br>MOSFET |

| $S_{LVDC}$ | 1<br>2 | Identical to $S_{AB}$ |                |          | 780           | 12.82<br>6.75     | HF    | SiC<br>MOSFET |               |

Table 3: Component count tipping points for Case 1.

| Component  | Number of Iso. Components $(M_{Iso}{=}10)$ | $V_{MVDC} \ (kV)$ when P.Iso. has fewer components |  |  |  |

|------------|--------------------------------------------|----------------------------------------------------|--|--|--|

| T.W.       | 252                                        | Always                                             |  |  |  |

| T.C.       | 30                                         | 22.62                                              |  |  |  |

| $S_{LVDC}$ | 120                                        | Always                                             |  |  |  |

| $S_{FB}$   | 888                                        | 17.16                                              |  |  |  |

| $S_{AB}$   | 888                                        | Always                                             |  |  |  |

| $L_f$      | 6                                          | Always equal                                       |  |  |  |

| $C_{MVDC}$ | 0                                          | Never                                              |  |  |  |

| $C_{LVDC}$ | 30                                         | 22.62                                              |  |  |  |

| $C_{FB}$   | 222                                        | 17.16                                              |  |  |  |

$V_{LVDC}=800\ V$ . The higher DC port voltage doesn't impact the number of components of any of the topologies as it is assumed that a single active bridge switch can block the  $V_{SM,AB}=800\ V$ .

The partially-isolated topology exhibits similar fundamental characteristics as for Case 1; requiring a higher number of components to support higher intermediate DC voltages. However, the lower AC port voltage can now be interfaced with a lower number of SMs (increasing from a baseline of  $N_{P.Iso} = N_{P.Iso,AC} = 12$  for  $V_{MVDC} = 0$  V).

Also similar to Case 1, two isolated topologies are pictured, which both require a higher number of CHB SMs  $N_{Iso}=10$  compared to a single arm of the MMC (when modulating  $V_{MVDC}=0~V$ ) due to the constraint of the CHB SMs to the active bridge voltage blocking ability. The number of MAB modules required is reduced compared to Case 1 due to the lower AC voltage.  $M_{Iso}=3$  represents the ideal configuration derived from eq 12 that groups four CHB SM-linked active bridge pairs proportionally to the number of LV DC portlinked active bridges according to the ratio of AC to DC port power (resulting in nine active bridges per transformer core). The number of active bridges per transformer core can now

Figure 11: Comparison of component numbers for Case 2:  $2x \ 5 \ kV$  AC DN ports and  $1x \ 800 \ V$  DC ESS port.

be reduced to five by increasing  $M_{Iso}=5$ .

The topologies exhibit similar relationships to one another as for Case 1 but now all topologies require a lower number of components (other than the fixed  $C_{MVDC}=1$  that could be sized lower for the lower intermediate DC voltages) due to the lower AC voltages. The two tipping points where the partially-isolated topology outperforms the  $M_{Iso}=3$  isolated configuration occur at  $V_{MVDC}=2.15\ kV$  and  $V_{MVDC}=6.24\ kV$  (detailed in Table 4). The higher tipping point operating condition again corresponds to a lower number of all components in the partially-isolated topology other than FB switches and capacitors.

The lower tipping point corresponds to a modulation ratio m=6.6 while the higher

Table 4: Component count tipping points for Case 2.

| Component  | Number of Iso. Components $(M_{Iso}{=}10)$ | $V_{MVDC} \ (kV)$ when P.Iso. has fewer components |

|------------|--------------------------------------------|----------------------------------------------------|

| T.W.       | 69                                         | Always                                             |

| T.C.       | 9                                          | 6.24                                               |

| $S_{LVDC}$ | 36                                         | Always                                             |

| $S_{FB}$   | 240                                        | 2.15                                               |

| $S_{AB}$   | 240                                        | Always                                             |

| $L_f$      | 6                                          | Always equal                                       |

| $C_{MVDC}$ | 0                                          | Never                                              |

| $C_{LVDC}$ | 9                                          | 6.24                                               |

| $C_{FB}$   | 60                                         | 2.15                                               |

tipping point corresponds to a modulation ratio m=2.3. The difference in modulation ratio is exaggerated due to the larger impact of the switch voltage blocking abilities on the lower AC and intermediate DC voltage levels. The lower tipping point modulation ratio now exists beyond the upper limit of explored modulation ratios in the literature and is deemed to be undesirably large.

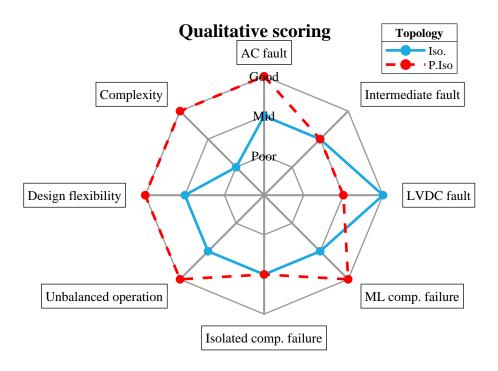

### 3.3.2 Qualitative Scoring of Topology Characteristics

The key operational characteristics of the two winning topologies for the ESOP MPC application are now compared in detailed. The characteristics are discussed in the following subsections before being qualitatively scored using a traffic light system (good/mid/poor) that is depicted in Figure 12.

The key characteristics for the ESOP application are:

- The impact of AC port, intermediate stage (MV DC bus or HF transformer), and LV DC port loss

- The impact of AC/DC converter and isolated stage component failure

- The ability to operate throughout unbalanced conditions

- Design flexibility and modularity

- Core coupling and control complexity

**Port Fault Tolerance (Loss of Port or the Intermediate Stage)** [24] (Chapter 5) explores the characteristics of a back-to-back MMC with DC load port in response to a range of port faults. The MMC is shown to be capable of riding through AC faults without passing critical fault dynamics to the intermediate DC bus but that the exact behavior of

the DC voltage, arm voltages, and total energy depends on the MMC's control approach. The FB MMC is shown to be capable of blocking a DC fault and therefore enabling continued AC STATCOM behavior when using crossed control. Active power could not be transferred between ports in the case of intermediate DC bus fault.

In the case of a LV DC port fault the ISOP DC/DC converter will likely need to be shutdown following the identification of a fault to reduce the transformer voltage to zero and denergize the LV side [7]. The intermediate DC bus may be able to remain energized and support back-to-back operation of the MMCs without access to the LV DC port. This MPC fault operation requires additional analysis.

The performance of the isolated topology during different port faults is explored in [24] Chapter 4. [24] highlights that the loss of either AC port impacts the fundamental power flow through the link CHB SMs and active bridges and therefore requires fault identification and a control mode shift. However, the isolated topology simply views loss of the LV DC port as a DC load change. Although the intermediate transformer stage failure is unlikely it would result in shutdown of the entire MPC.

**Component Failure Tolerance** The partially isolated topology is resilient to MMC SM failure due to their ability to be bypassed. Additionally, the parallel components of the ISOP DC/DC stage offer redundancy. However, the ISOP stage will be sensitive to active bridge failure on the input-series side of the DC/DC converter.

The isolated topology is less resilient to CHB SM failure due to their direct linkage with the MAB SMs. The failure of these components will impact MAB power flow and SM balancing but is manageable due to the many redundant paths below rated operation. Failure of LV active bridge components shouldn't significantly impact the converter's capacitor balancing.

**Performance in Unbalanced Conditions** The partially-isolated topology's MMC can utilize circulating current, energy balancing, and negative sequence controllers to suppress the second harmonic current that results from unbalanced conditions [25]. These controls minimize the impact of unbalanced conditions on the intermediate DC bus and hence the MPC.

The isolated topology is sensitive to unbalanced conditions, where the coupling of all ports through the HF transformer can result in the transfer of power oscillations. Oscillations can be mitigated with the addition of negative sequence controllers [24] (Chapter 4).

**Design Flexibility/Modularity** The FB MMC of the partially-isolated topology is flexible to support different MV AC voltages either with the variation of the modular SMs or directly using a fixed configuration and varying the insertion of SMs. The flexibility of the FB MMC is particularly relevant in the case of an ESOP that interfaces two different AC voltage

levels, where either different MMC configurations can be used for the different ports or identical MMCs can be used with varying modulation ratios. The ISOP stage also has a relatively modular configuration that can be varied to support different intermediate DC voltage levels.

The CHB and multi-MAB isolated configuration also has the ability to be reconfigured for different voltage characteristics but will require significant rewiring to do so.